# User Hardware Handbook CENTRAL PROCESSOR UNIT CONTROLS AND MONITORING

# GEC Computers Limited 1977

The information presented herein is, to the best of our knowledge, true and accurate. No warranty or guarantee, expressed or implied, is made regarding the accuracy of information supplied or capacity, performance or suitability of any product or service since the manner of use is beyond our control.

You are advised that you should ensure that the information contained herein has not been superseded.

All our products, materials and services are sold subject to our Conditions of Sale, available on request.

GEC COMPUTERS LIMITED

Elstree Way, Borehamwood, Hertfordshire.

Telephone No. 01-953-2030

Holding Company - the General Electric Company Limited of England

# CPU CONTROLS AND MONITORING

|            |        |                |             |             |     | JUNI | CIN   | 13  |     |     |            |     |      |       |        |           |            |      |     |      |     | Dama      |

|------------|--------|----------------|-------------|-------------|-----|------|-------|-----|-----|-----|------------|-----|------|-------|--------|-----------|------------|------|-----|------|-----|-----------|

| <b>1</b> . | INTR   | ODUCTION       |             |             |     |      | •••   | ••• |     | ••• |            | ••• |      |       |        |           | •••        | •••  |     |      |     | Page<br>1 |

| 2          | BASI   | C CONTROLS     |             |             | ••• | •••  |       |     | ••• |     |            |     |      |       |        |           | • 5        |      |     |      | ••• | 2         |

|            |        | ON/OFF         |             |             |     |      |       |     |     |     |            | ,   |      |       |        | ٠.        |            |      |     |      |     | 2         |

|            |        | Panel Mode S   |             |             |     | 1 -  |       |     |     |     |            |     |      | . *** | 100    |           |            | : '. | •   |      | * % | 3         |

|            |        | Reset , Run an |             |             |     |      |       |     |     |     |            |     |      |       |        | V         |            |      |     |      |     | 3         |

|            |        | IPL            |             |             |     |      |       |     |     |     | <i>.</i> . |     | ** 1 |       |        |           |            | (41) |     |      |     | 4         |

|            |        | IPLAs          |             |             |     |      |       |     |     |     |            |     |      |       |        | , 13<br>1 | 5.3        |      |     |      |     | 5         |

|            | 2.5    | IF LAS         | •••         | <br>        | ••• | ***  | • ••• | ••• | ••• | ••• | •••        | ••• | •••  |       | • . •• |           | •••        | ···· | *** | •••  | ••• |           |

| 3          | MONI   | TOR LAMPS      | AND C       | ATA         | SV  | VITC | HES   | 3   | ••• |     |            | ••• | •••  |       |        |           | •••        |      | ••• | •••  | ••• | 6         |

|            | 3.1    | General        |             | · · · · · · |     |      |       |     | ••• | ••• | •••        | ••• | •••  | ·•• • |        | • ••      |            |      | •   | •••  | •   | 6         |

| a'         | 3.2    | Method of Mo   | nitorin     | ıg          |     |      |       |     | ••• | ••• | •••        |     | •••  |       |        |           | •••        | •••  |     |      |     | 6         |

|            |        |                |             |             |     |      |       |     |     |     |            |     |      |       |        |           |            |      |     |      |     |           |

| 4          |        | NEER'S CON     |             |             |     |      |       |     |     |     |            |     |      |       |        |           |            |      |     |      |     | 8         |

|            |        | Control Keys   |             |             |     |      |       |     |     |     |            |     |      |       |        |           |            |      |     |      |     | 8         |

|            | 4.2    | Lamps          |             | •••         | ••• |      | • ••• | ••• | ••• | ••• | •••        | ••• | •••  |       | ••••   | • ••      | •••        | ٠    | ••• | •••  | ••• | 9         |

|            | 4.3    | Manual Test I  | <b>Ceys</b> | •••         | ••• |      |       | ••• | ••• | ••• | •••        | ••• | •••  |       |        |           |            | •••  | ••• | •••  | ••• | 9         |

|            | 4.4    | Test and Stop  | Mode        | Switc       | hes |      |       | ••• | ••• | ••• | •••        |     | •••  | ••••  |        | • ••      |            | •••• | ••• | •••• | ••• | 10        |

|            | 4.5    | Test Mode Sw   | itch        |             | ••• |      |       | ••• | ••• | ••• | •••        |     | •••  |       |        |           |            | •••  | ··· | •••  | ••• | 11        |

| 5          | LISAC  | SE OF CONTR    | n s         |             |     |      |       |     |     |     |            |     |      |       | -      |           |            |      |     |      |     | 13        |

| •          |        | Basic Controls |             |             |     |      |       |     |     |     |            |     |      |       |        |           |            |      |     | •••  |     | 13        |

|            |        |                |             |             |     |      |       |     |     |     |            |     |      |       |        |           |            | •••  | ••• | •••  | ••• | 13        |

|            | 5.2    | Basic Controls | . WILLI     | -riyiti     |     | COI  | 11 01 |     | ••• | ••• | •••        | ••• |      | •••   | ••••   | •         | • •••<br>· |      | ••• | •••  | ••• | 13        |

|            |        |                |             |             |     | TA   | BLI   | ES  |     |     |            |     |      |       |        |           |            |      | ÷   |      |     |           |

|            |        |                |             |             |     |      |       |     |     |     |            |     |      |       |        |           |            |      |     |      |     |           |

| Table 1:   | Data I | Monitoring     | •••         | •••         | ••• | •••  | • ••• | ••• | ••• | ••• | •••        | ••• | •••  | •••   | •• •   | •         |            | •••  | ••• | •••  | ••• | 18        |

| Table 2:   | Addre  | ess Monitoring |             |             |     |      |       |     | •   | ••• |            | ••• |      |       |        |           |            |      |     | •••  |     | 19        |

|           |                                              | Page                  |

|-----------|----------------------------------------------|-----------------------|

| Table 3:  | Instruction Decode Brd. 109 and ROMAD Bd 101 | 20                    |

| Table 4:  | Control A                                    | 20                    |

| Table 5:  | Control B                                    | 21                    |

| Table 6:  | Timer,                                       | 21                    |

| Table 7:  | Main Register Control                        |                       |

| Table 8:  | Conditions                                   | and the second second |

| Table 9:  | Data Monitor Highway                         | 23                    |

| Table 10: | Address Highway (BMC)                        | 24                    |

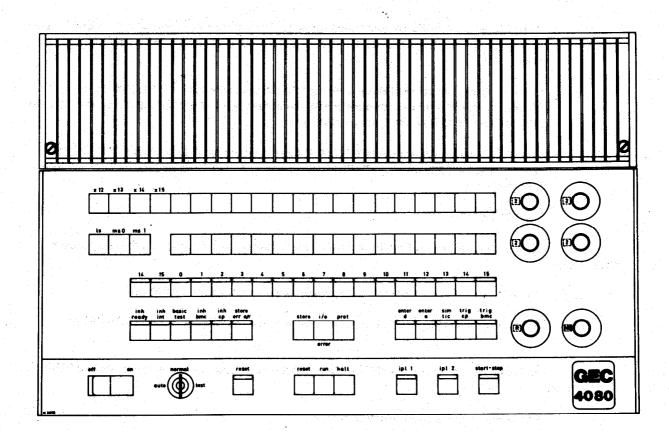

The Control and Monitoring Unit (CMU) comprises the lower half of the CPU front panel assembly, and consists of control switches and indication lamps mounted, with their associated circuitry, on a printed circuit board at the rear of the front panel.

Connections are taken from the board by a lighweight cable to three top edge connectors on the Control Monitor card in the logic rack.

The controls and lamps are split into five rows; which are, reading from bottom to top.

| .л. (a) · | Basic Controls:-                   | Controls necessary to operate the equipment Normally used for ON/OFF operation. |

|-----------|------------------------------------|---------------------------------------------------------------------------------|

| (b)       | Engineers Controls:-               | Used for Commissioning or maintenance purposes.                                 |

| (c)       | 20 Data Keys (18:4080):-           | Data source for program including IPL, and manual tests.                        |

| (d)       | 19 Data Highway Monitor<br>Lamps:- | Display data words on highways selected by rotary switches DA and DB            |

| (e)       | 20 Address Highway Monitor Lamps:- | Display address words on highways selected by rotary switches AA and AB.        |

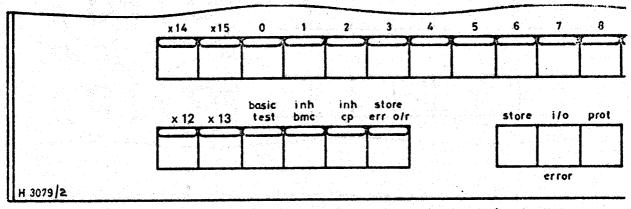

**4080 CMU PANEL**

| off      | on normal     | reset | reset run halt |

|----------|---------------|-------|----------------|

|          | auto (1) test |       |                |

|          |               |       |                |

| H 3079/2 |               |       |                |

## 2.1 ON/OFF

The ON/OFF switch is a rocker switch which controls the mains supply to the unit. If switched to the ON position, AC mains is provided via a cable at the rear of the unit to a MAINS DISTRIBUTION UNIT (MDU) where a relay is energised to switch mains supply to the Power Supply Unit of the CPU and to other units (stores, peripherals, etc.) in the system. If switched to the OFF position, AC mains is removed from the MDU which in turn opens the relay to remove mains from the CPU and other units powered from it.

NOTE One side of the mains switch remains alive.

Switch ON

When the CPU is switched on by the application of mains supply to the PSU, the following sequence takes place:-

- (a) When DC rails in the CPU are established correctly the machine will be placed in the RESET state with the HALT and RESET lamps illuminated, STORE ACTIVE and ACTIVE signals will be held false.

- (b) When the Rails Correct (RC) signal from the PSU becomes true and INTERLOCK is true (indicating that other units within the configuration have powered-up correctly) then after 200 ms ACTIVE and STORE ACTIVE will be made true.

- (c) If when DC rails are correct the INTERLOCK signal is false, then ACTIVE and STORE ACTIVE remain false until 200 ms after INTERLOCK goes true. ACTIVE and STORE ACTIVE are then both made true.

#### Switch OFF

If the CPU is switched off by the removal of mains supply from the PSU, the following sequence takes place:-

- (a) The ACTIVE signal is taken false and a 'Power Fail' Error interrupt is generated.

- (b) After 1 ms the STORE ACTIVE signal is made false and the machine is placed in the RESET state.

The same actions occur if the INTERLOCK signal is taken false, indicating Power Failure elsewhere in the system.

For further details see CPU Nucleus manual.

#### 2.2 PANEL MODE SWITCH

Adjacent to the ON/OFF switch is a 3-position key operated switch enabling the panel to be used in one of three modes.

(a) Normal

The basic controls and Data Keys are operative.

(b) Test

All controls are operative.

(c) Auto

The ON/OFF control only is operative. Switch-on causes an automatic program start by placing the machine in the RUN state. No Initial Program Lead (IPL) sequence is possible.

# 2.3 RESET, RUN AND HALT LAMPS AND SWITCHES

# Reset

The RESET lamp is illuminated if the machine is halted (with the HALT lamp illuminated) and is in its quiescent reset state.

If the machine is not in the RUN state (e.g. the RUN lamp is extinguished) it may be placed in the RESET state by depressing the RESET key. This has the effect of

- (a) Placing the clock in its reset state if it was stopped by a 'Busy' condition.

- (b) Resetting interfaces by taking the ACTIVE and STORE ACTIVE interface lines false for at least 200 ms.

- (c) Resetting the internal logic of the CPU and BMC.

# Start/Stop

The RUN lamp is illuminated if the internal clock of the machine is running; whilst the HALT lamp is illuminated if the clock is stopped in its reset state. If the HALT lamp is illuminated and the RESET lamp is extinguished the machine is in the HALT state.

(a) If the START/STOP key is depressed whilst the machine is in the RUN state the CPU/BMC is put into the HALT state at the end of the current CPU instruction or BMC cycle. Depressing the START/STOP key whilst the machine is in the HALT state causes operation to be resumed with the next-instruction in sequence and/or the next BMC cycle in sequence.

- (b) If the START/STOP key is depressed whilst the machine is in the RESET state the machine is put into the RUN state and one of the following initial start sequences is performed:-

- (i) with the panel in NORMAL or the BASIC TEST key up (i.e. in full nucleus mode) a 'load HSR' operation is performed, followed by a nucleus reschedule.

- (ii) with the panel in TEST and the BASIC TEST key depressed an entry is made to the interrupt level, with the cause code set to 13<sub>10</sub> (in store location 0)

NOTE If the machine is in RESET with INTERLOCK held false, depressing START/STOP will have no effect.

## **Operation in Auto**

If the CMU is switched to AUTO mode the START/STOP and RESET keys are inoperative. The machine is placed in the RESET state after switch on (as described in 2.1.1.) or after power failure (as described in 2.1.2.). After ACTIVE and STORE ACTIVE have been made true, an automatic START signal is generated by the processor, which has the same effect as depressing the START key with the machine in RESET.

If the machine is in AUTO, it can only be halted by switching its mains power off, or by breaking the INTERLOCK signal to the CPU (see 2.1.b)

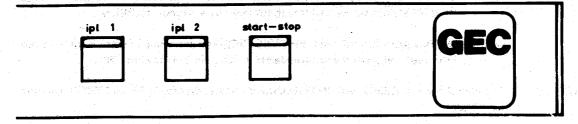

#### 2.4 IPL

The Initial Program Load facility of the processor provides a method of loading software into an empty machine, and triggering its execution.

The facility is performed by copying a short 'Initial Input' program, into store, from ROMs mounted on exchangable IPL Assemblies (IPLAs). The initial input program is then actioned to load software into store from a selected input device.

Two IPLAs may be fitted to provide a choice of IPL from alternative types of device. The IPLAs are easily exchanged, allowing the selection of input device to be varied.

# **IPL Sequence**

The IPL sequence is initiated by depressing either of the IPL keys (IPL1 or IPL2) on the CMU panel. For this to be effective:-

- (a) The CMU must be in the RESET state (HALT and RESET lamps lit).

- (b) The CMU panel must be in NORMAL or TEST.

If both of the above conditions exist the sequence is as follows:-

- (i) The processor is forced into BASIC TEST mode, regardless of the state of the BASIC TEST key on the front panel.

- (ii) An Initial Input Program is copied into Store locations 0 upwards, from IPLAs. One of two possible programs is loaded depending on whether IPL1 or IPL2 is selected.

- (iii) The Initial Input program is now triggered at interrupt level such that the contents of locations 22 and 24 in Store are loaded into the Sequence Register and Local Register respectively.

- (iv) The Initial input program is now executed, and will normally read program and data from an appropriate input device, triggering the system it has loaded.

#### 2.5 IPLAs

The ROMs containing the Initial Input programare on two IPLAs, mounted on the top edge (EC5 and EC6) of the Arithmetic board of the CPU. Each IPLA provides up to 128 bytes of Initial Input program. In the following pages the IPLA on EC5 will be called Assembly A and that on EC6, Assembly B.

If key IPL1 is depressed, the content of Assembly A is loaded into bytes 0-127 of Store, the other locations in store being unchanged; whereas if key IPL2 is depressed, the content of Assembly B is loaded into bytes 0-127 of Store and the content of Assembly A is loaded into bytes 128-255.

#### 2.6 USAGE

Loading of the IPLAs by use of keys IPL1 and IPL2 may be executed in three ways.

- (a) With only one IPLA fitted (Assembly A on EC5) IPL1 is always used and IPL is available only from one device.

- (b) With both IPLAs fitted independent Initial Input programs from two different devices can be held.

IPL1 and IPL2 can then be used to select which Initial Input program (A or B) is to be used.

- (c) With both IPLAs fitted they can be employed to hold a single program for a more complex device. In this instance key IPL2 must always be used to load both IPLAs.

## Loading of Full Nucleus Systems

Operation of either of the IPL keys forces the machine into Basic Test mode. When loading of the full Nucleus system is completed, it is necessary to switch the machine to full nucleus mode to commence execution. The two methods of achieving this are:-

- (a) Stop the machine at completion of loading, by operation of the START/STOP key or by a HRK instruction. Ensure that the BASIC TEST key is in the up position, or that the CMU is in NORMAL mode.

- Press the RESET key to assert the Full Nucleus mode, and then press the START/STOP key to start the machine running. A Nucleus reschedule operation will be performed and system software will be entered.

- (b) By obeying a SFN (Set Full Nucleus) instruction. This sets Full Nucleus Mode, provided that the BASIC TEST key is in the up position or that the CMU is in NORMAL, thus causing a Nucleus reschedule to enter the Full Nucleus system.

#### 3.1 GENERAL

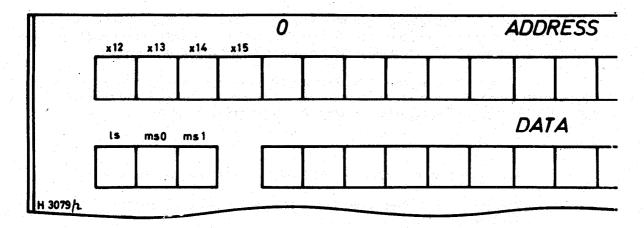

The three rows of monitoring lamps and data keys are aligned so that the corresponding bits are directly beneath one another.

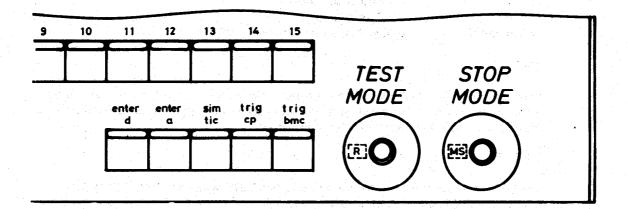

The data keys (Figure on pages 8 and 9) have four functions:-

- (a) As a source of data for input to the data registers. Keys labelled 0-15 provide the 16 data bits.

The keydata is routed onto the appropriate data highway via the data lines from store.

- (b) As a source of data for input to address register, enabling all stores to be directly addressed in half words. Keys are labelled as follows:

4080:

X14, X15, 0-15 provides a full 18 bit addressing,

4070:

X13,X14, X15, 0-15 provides a full 19 bit addressing,

- 4082: X12, X13, X14, X15, 0-15 provides a full 20 bit addressing.

- (c) As a source of data used as a standard to compare with address selected data (see Usage of Engineers Controls).

- (d) As a source of data for the RK (Read Keys) and HRK (Halt and Read Keys) instructions. If the machine is in Auto, the Data Switches act as a source of zeros.

There are 20 Address Monitoring Lamps designated x12 - x15, 0 - 15. The 20 bits are necessary to display base and range registers simultaneously.

The 19 Data Monitoring Lamps are split into 2 groups:-

- (a) Labelled 0 15 for 16 bit and other data registers.

- (b) Labelled is, ms0 and ms1 for information on register end effects (shifts, carries, etc.).

# 3.2 METHOD OF MONITORING

A large number of points are monitored by the built-in facilities enabling fault diagnosis to be made fairly accurately.

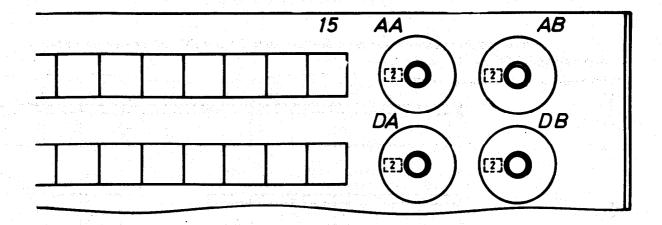

Most boards may place data/control waveforms onto either or both of two monitoring highways with the lamps directly displaying their logic state.

Data to be placed on a highway is selected by two 8-way switches mounted beside each row of monitoring lamps enabling up to 64 words to be monitored.

# **Address Highway Monitoring**

The highway is 20 bits wide and monitors address registers and control waveforms. For details see Tables 1-10.

# **Data Highway Monitoring**

The highway is 19 bits wide and monitors data registers and control waveforms. For details see Tables 1-10.

# Monitoring in RUN State

Tables 1-10 list the Register and Control waveforms when the machine is in the HALT state.

When the machine is in the RUN state the following registers cannot be monitored as they share highways. Setting the switches to one of these registers selects the appropriate common highway.

| AL,AM, BL, BM<br>L, S, X, Y, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Data monitor highway switch setting 50 (main Reg.) selects common highway for these registers. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| w <sub>1</sub> , w <sub>2</sub> , w <sub>3</sub> ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                |

| 2. 医多数300 电线电流 100 to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 대학교는 아무리는 이 책임에 이 사는 사람이 회에 가진하는 것이 되었다.                                                       |

| $\mathbf{Q}_{\mathbf{z}}^{-1}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Data selection switch setting = 51 selects common                                              |

| 1 - 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Q reg. highway                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20.12                                                                                          |

| U <sub>1 - 4</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Data selection switch setting = 62 selects common                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U reg. highway.                                                                                |

| 1 The second of the second |                                                                                                |

#### **ENGINEER'S CONTROLS**

The annotations shown are related to 4070 and 4082. On the 4080  $\times$  12 is marked INH.READY and  $\times$  13 is INH. INT. refer to Figure on page 1.

A comprehensive set of controls are provided. These are described individually in this Section. Their usage is described in Section 5. As mounted on the front panel they form a row beneath the data keys.

## 4.1 CONTROL KEYS

A group of 6 keys on the lefthand side of the panel inhibit certain facilities for test purposes. They are only active in the test mode.

## INHIBIT READY (4080 only)

A locking control that in the down position prevents the BMC from servicing any external readies.

#### INHIBIT INTERRUPT (4080 only)

A locking control that in the down position inhibits all interrupts from the BMC and Command Interface.

#### **BASIC TEST**

A locking control that in the down position locks out the segmentation feature and replaces the other nucleus features with a few simple I/O instructions. The BASIC TEST switch is depressed when certain simple test programs are to be run.

#### INHIBIT BMC

A locking control which in the down position prevents the BMC from operating by inhibiting all BMC Clocks.

#### **INHIBIT CPU**

A locking control which in the down position prevents the central processor from operating by inhibiting all CPU clocks.

#### STORE ERR O/R

A locking control which in the down position prevents the CPU or BMC from taking any action on time out or parity errors.

#### 4.2 ERROR LAMPS

A group of 3 lamps that indicate an error has occurred. They are lit independently of any action the CPU or BMC may take.

#### STORE ERROR

The lamp is lit whenever a store parity or timeout error occurs giving a visual record of failure. It is extinguished by placing the machine in the HALT state.

#### I/O ERROR

The lamp is lit when the BMC has detected an error. It is extinguished by placing the machine in the HALT state.

#### PROT. ERROR

If the CPU attempts to address store in violation of the hardware protection circuitry the lamp will be lit. It is extinguished by placing the machine in the HALT state.

# 4.3 MANUAL TEST KEYS

A group of 5 keys mounted to the right of the error indicator lamps. These are all non-locking and only operate in the test mode.

# **ENTER D**

The key is only operative when the machine is in the HALT, state. When depressed data (bits 0-15 from the data keys) is entered into a register selected by the data selection switches. The following registers may be loaded

Am, Al, Bm, Bl, S, L, X, Y, Z W1, W2, W3 Q1, Q2, Q3, Q4 U1, U2, U3, U4

# **ENTER A**

The key is only operative when the machine is in the HALT state. When depressed data (bits X14, X15, 0-15) from the data keys is entered into an address register selected by the address selection switches.

The following registers may be loaded:

IA

- Instruction Register

VA

- Virtual Store Address

**ROMAD**

- R.O.M. Address

**BMC ROMAD**

- Basic Multiplexer Channel R.O.M. Address

#### SIMTIC

Only operative in the HALT state. When depressed it clocks data into the F and G latches at the output of the arithmetic unit. When stepping through the microprogram it may be used for checking data routing through the shifter to the register.

#### TRIG CP

This key is only operative when the machine is in the RESET state, and BASIC TEST mode is selected. the CPU enters the RUN state and actions the next instruction in sequence if the TRIG CP switch is held down whilst the START/STOP key is depressed.

In all other circumstances the TRIG CP key has no effect.

#### TRIG B.M.C.

When depressed it causes the CPU to simulate a direct output to the BMC. For details of usage see Section 5. The key is not operative when the CPU is in the RESET state.

## 4.4 TEST AND STOP MODE SWITCHES

#### STOP MODE SWITCH

The 8-position switch controls the operation of the clock. The switch should only be operated when the machine is in the HALT state.

| ABBREVIATION | POSITION | FUNCTION                                                                                                                                                                                                                                          |

|--------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0            | <b>1</b> | OFF This position allows continuous operation of the clock, which can only be stopped by operation of the START/STOP key.                                                                                                                         |

| IS .         | 2        | INST. STEP The clock is stopped (placed in HALT state) at the end of an instruction (or BMC transfer) With the machine in the HALT state every depression of the START/STOP key will cause an instruction and/or BMC transfer cycle to be obeyed. |

| MS           | 3        | MICROSTEP With the machine in the HALT state every depression of the START/STOP key causes the CPU and/or BMC to execute one step of the microprogram (see NOTE)                                                                                  |

| 10           | 4        | I/O ERROR STOP  If the BMC detects an I/O error the clock is stopped at the microstep and the I/O ERROR and HALT lamps light.                                                                                                                     |

| ABBREVIATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | POSITION                              | FUNCTION                                                                                                                           | <del></del>                        |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|

| ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5                                     | STORE ERROR STOP                                                                                                                   |                                    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | The clock is stopped and HALT lamp lit if a store parity or timeout error is detected. On restart, by                              |                                    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | depressing START/STOP the machine bran<br>to error routine. If the ERROR override ke<br>the machine may be restarted in the normal | ine branches<br>erride key is down |  |  |  |  |

| SN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                                     | SYNC. STOP                                                                                                                         |                                    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | The clock is stopped and HALT lamp lit if the data                                                                                 |                                    |  |  |  |  |

| and the second of the second o | · · · · · · · · · · · · · · · · · · · | in a pre-selected register is identical with the setting                                                                           |                                    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | of the data keys. The data to be compared is determined by the setting of the address selection switch                             |                                    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | The facility is available for                                                                                                      |                                    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | SA - Store address                                                                                                                 | 23                                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | VA - Store virtual address                                                                                                         | 21                                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | BMC SA - BMC store                                                                                                                 | 70                                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | IA - CPU Instruction Register                                                                                                      | 41                                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | ROMAD - ROM Address Register                                                                                                       | 27                                 |  |  |  |  |