# GEC COMPUTERS LIMITED

# USER HARDWARE HANDBOOK - SYSTEM ENGINEERING (SYSTEM DESCRIPTION)

# © GEC Computers Limited 1974

The information presented herein is, to the best of our knowledge, true and accurate. No warranty or guarantee, expressed or implied, is made regarding the accuracy of information supplied or capacity, performance or suitability of any product or service since the manner of use is beyond our control.

You are advised that you should ensure that the information contained herein has not been superseded.

All our products, materials and service are sold subject to our Conditions of Sale, available on request.

GEC COMPUTERS LIMITED

Elstree Way, Borehamwood, Hertfordshire.

Telephone No. 01-953-2030

A subsidiary of the General Electric Company Limited.

# CONTENTS

|          | Pag                                                         | je       |

|----------|-------------------------------------------------------------|----------|

| <b>i</b> | INTRODUCTION TO HARDWARE USER HANDBOOK - SYSTEM ENGINEERING | 1        |

|          |                                                             |          |

| 2 .      | 4080 CONFIGURATION - INTRODUCTION                           | )        |

|          | 2.1 Configuration                                           | <b>?</b> |

|          | 2.2 Overall Structure                                       | 2        |

|          | 2.3 Implementation                                          | 2        |

|          | 2.4 Subjects for Consideration                              | 5        |

| 3        | WAY NUMBERS AND READY NUMBERS                               | 8        |

|          | NORMAL INTERFACE LOADING                                    | 9        |

|          |                                                             | 9        |

|          | 4.1 Scope                                                   | •        |

|          | 4.2 General Considerations                                  | 9        |

|          | 4.3 Simple Rules for Interface Loading and                  | 0        |

|          |                                                             |          |

| 5        | SLOT ALLOCATION RULES                                       | 3        |

|          | 5.1 Central Processor                                       | 3        |

|          | 5.2 Extension Unit                                          | 3        |

|          | 5.3 Board Positioning                                       | 4        |

| 6        | OVERLOAD EFFECTS                                            | 16       |

| 6        |                                                             | 16       |

|          | O. I. Interval filler                                       |          |

|          | 6.2 Magnetic Tape Controller                                | 16       |

|          | 6.3 Card Reader Controller                                  | 16       |

|          | 6.4 Cartridge and HPT Discs                                 | 16       |

|          | 6.5 Paper Tape Reader (500) and Punch (110)                 | 16       |

|          | 6.6 Teleprinter Controller (ASR33)                          | 16       |

|          | 6.7 Line Printer (300/136 and 600/136)                      | 16       |

|          | 6.8 Watchdog and Interrupt Unit                             | 16       |

|          | 6.9 Modem Interfaces                                        | 17       |

# TABLES

|               |                                              | Page |

|---------------|----------------------------------------------|------|

| Table 1:      | Percentage Loads and Limiting Times          | 11   |

| Table 2:      | Typical System Configuration                 | 12   |

|               |                                              |      |

|               | IN-TEXT FIGURES                              |      |

| Figure 1:     | Basic 4080 System                            | 3    |

| Figure 2:     | 4080 System with Extension Unit and IOP      | 4    |

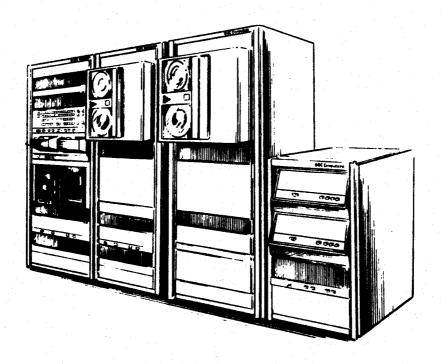

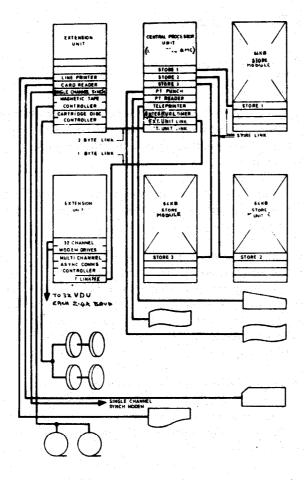

| Figure 3:     | Typical System Configuration - Pictorial     | 6    |

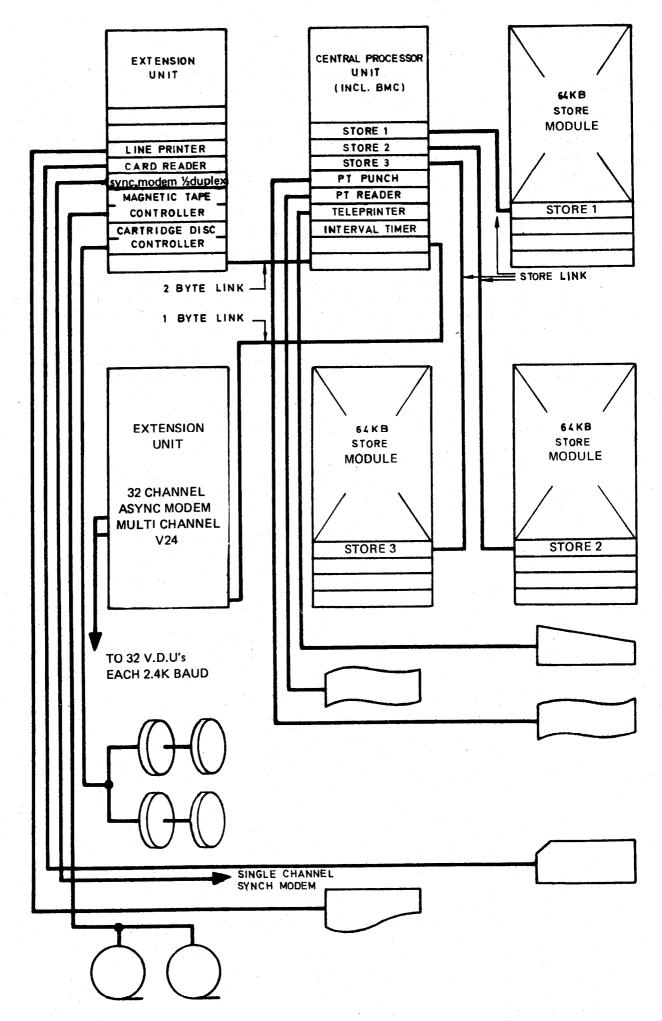

| Figure 4:     | Typical System Configuration - Block Diagram | 7    |

|               |                                              |      |

|               | SUPPLEMENTS                                  |      |

| Supplement 1: | List of Units                                |      |

| Supplement 2: | Ready Number Allocation                      |      |

# I INTRODUCTION TO HARDWARE USER HANDBOOK - SYSTEM ENGINEERING

The System Engineering Handbook is structured to provide a system engineer with basic information necessary to gain an overall appreciation of the GEC 4080 computer system. This basic information is expanded to include all the information required to plan, and arrange for, the installation of a complete configuration (system) or any of its units.

The Handbook comprises the following manuals, each of which covers a distinct aspect of the subject.

System Description Manual (This manual.)

Installation and Standards Manual

Interfaces Manual

**Processor Performance Manual**

2

# **4080 CONFIGURATION - INTRODUCTION**

#### 2.1 CONFIGURATION

A GEC 4080 configuration consists of standard units supplied by GEC Computers Ltd., supplemented as necessary by other GEC products (e.g. March 4 process peripherals), or by user supplied equipment. The standard GEC units are listed and briefly described in Supplement 1.

The GEC 4080 and its associated equipment may be assembled into a wide variety of possible configurations. This manual is intended to provide the basic information needed by the designer of such configurations. Details of the operation of particular interfaces or particular units are not included here, and may be found in the manuals relating to those interfaces and units.

# 2.2 OVERALL STRUCTURE

The central item in a 4080 system is the Central Processor Unit (CPU). The Basic Multiplexer Channel (BMC) used for the attachment of peripheral controllers, is an integral part of the C.P.U.

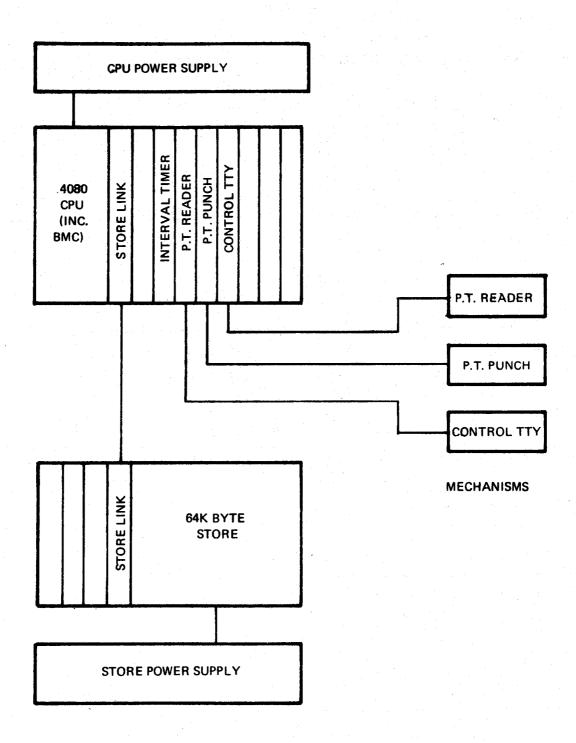

A simple 4080 configuration is shown in Figure 1. The CPU may be attached to several store units by individual store links. It is also attached to several peripheral controllers by the bus-connected Normal Interface. Most peripheral controllers are attached to one or more peripheral mechanisms.

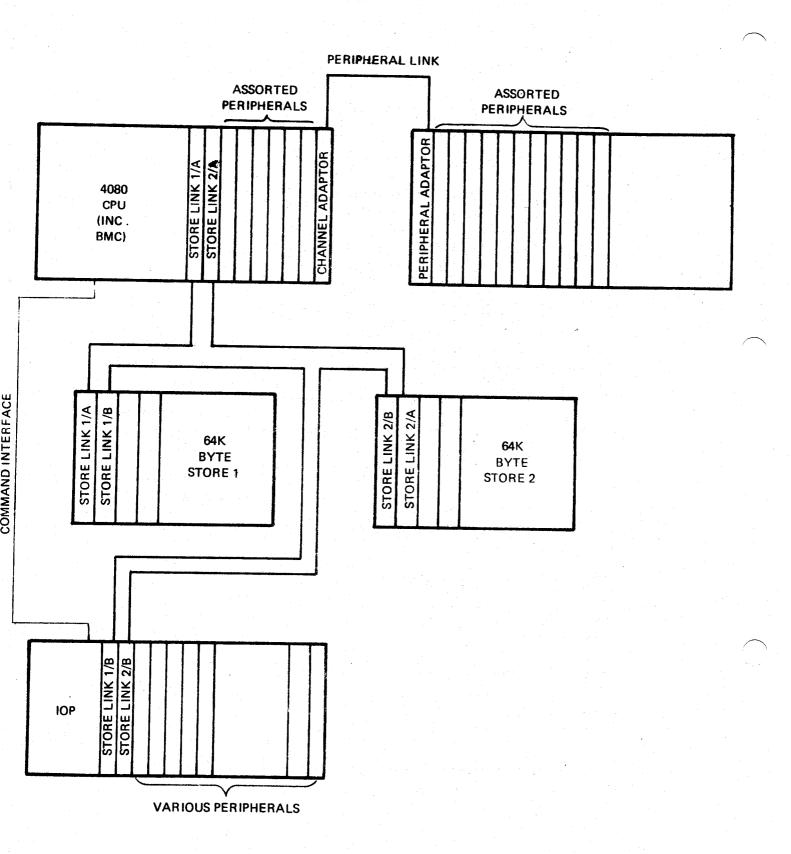

If more peripheral throughput is needed, one or more Input/Output Processors (IOP) may be fitted. The standard IOP called the External Multiplexer Channel (EMC) produces an independent Normal Interface to which further peripheral controllers can be attached. An IOP must be connected to the processor unit, via the Command Interface, and to each store via individual store links. Figure 2 shows a system with an IOP.

# 2.3 IMPLEMENTATION

Processor

The 4080 processor and BMC form a rack-mounting unit, containing logic boards. An independent rack-mounted unit contains the power supply unit.

Several spare board positions (or 'slots') are provided. Logic boards plugged into appropriate slots have access to the store interface, or the Normal Interface.

Stores

Each store unit consists of a rack mounting unit with an independent rack mounted power supply unit.

A store link connects the store to the processor. The link consists of one board that plugs into the store unit, connected by a detachable cableform to one board which plugs into a slot in the processor unit. A store may accommodate up to four store links, the additional three being available for connection to IOP's.

Figure 1: BASIC 4080 SYSTEM

NOTE As drawn the IOP has priority over the CPU in Store 1, and vice versa in Store 2

Figure 2: BASIC 4080 SYSTEM

# Peripheral Controllers

Each peripheral controller consists of one or more logic boards. These are connected by a detachable cableform to the associated peripheral mechanism, and obtain access to the Normal Interface by being plugged into a slot. This slot may be in the processor, or in the IOP if one is fitted. Since the number of slots so available is limited, additional slots are provided by Extension Units, described below.

#### Extension Units

An extension unit is used to provide additional slots for peripheral controllers. The extension unit is rack mounted, and has an integral power supply unit.

The extension unit must derive its Normal Interface directly or indirectly from the processor or IOP. A link occupies a dedicated board position in the extension unit, and is connected by a detachable cable-form to a board which plugs into a slot where the interface is already available. These may be used in series i.e. plugged into another extension unit instead of directly to the processor or IOP. The use of links in series is generally to be avoided for peripherals with high data rates, since it inevitably increases cycle times and hence interface loading.

#### Switched Extension Units

An extension unit may be fitted with one or more additional links, so that it can be connected to more than one system, but only one such link can be operational at a time. An externally controlled switch selects which link shall be operational. Note that the additional links differ slightly from standard links, and each occupies a slot in the extension unit which would otherwise have been available for a peripheral controller board.

# 2.4 SUBJECTS FOR CONSIDERATION

The remainder of this manual gives more detail of a number of subjects effecting configuration. This subsection provides an overview, so that the interrelationship of the various parts may be seen.

#### Mains Distribution and Switching

Mains power must be provided to all power supply units, to logic racks for fans, and to peripheral mechanisms. The distribution and switching system is described in Installation and Standards manual.

#### Cabinet Space Allocation

The various rack mounting units must be assembled into cabinets, with blanking panels where necessary, and with regard to cabling and ergonomic considerations. Additionally, possible interactions between units must be taken into account. Details are given in the Installation and Standards manual.

#### Store Interconnection

The rules for store interconnection are straightforward. The processor unit must be linked to each store unit, and any IOP must be linked to the required store units. Address patches are set up on the store links to define the starting address of the store for the processor using the link. The C.P.U. must be capable of addressing all store units, IOP's need to access store 0 for control information. The store interconnection system is described in the Interface Manual.

# Peripheral Devices

The arrangements for connecting peripherals to a 4080 system allow great flexibility, and allow large numbers of peripherals to be fitted. Inevitably, many interrelated aspects must be considered.

#### The major aspects are:

The allocation of peripheral controllers to slots in processors, and extension units, and the provision of links. Numbers of slots, power limitations and cable lengths must all be considered.

The allocation of relative priorities to peripherals, and consequent setting of Ready numbers. This is related to the permissable interface throughput calculation, and to the allocation of slots.

The allocation of Way Numbers for peripheral selection.

Availability of standard or test software for peripherals, and for related requirements for other peripherals or for particular amounts of store.

These various aspects are considered in details as follows:

Slot allocation and d.c. power limitations-Section 5 of this manual.

Cable lengths and a.c. power limitations - Installation and Standards Manual.

Allocation of Way Numbers--Section 3 of this manual.

Allocation of priority to various peripherals, and hence Ready number allocation— Section 4 and Supplement 2 of this manual.

Input Output Processor

Data is to be found in the System section of the appropriate IOP manual. That document also provides information on the differences in interface loadings when a peripheral controller is connected to an IOP rather than to the BMC.

Figure 3: TYPICAL SYSTEM CONFIGURATION - PICTORIAL

Figure 4: TYPICAL SYSTEM CONFIGURATION - BLOCK DIAGRAM

3

# WAY NUMBERS AND READY NUMBERS

Peripheral controllers are connected to either the BMC or IOP via the Normal Interface (See Interfaces Manual). Each peripheral and each link to an extension unit occupying slots in a particular processor rack, must have a patched Ready number in the range 0 to 15, and a corresponding Ready line. These Ready numbers determine the allocation of interface cycles to the various peripherals and links, Ready 0 having the highest priority. The Ready number and line or link is set by means of a changeable patch panel on the board concerned.

The single Ready number available to a link is sub-multiplexed so that 8 or 16 Ready lines and Ready numbers are available on the secondary interface within the extension unit.

In addition to a Ready number, or numbers, a Controller is allocated one or more Way numbers in the range 0 to 255. The Way numbers provides a unique identification for the controller and enables the BMC to identify the area of core store associated with the controller. Way and Ready numbers are patched onto the controllers by means of small printed circuit boards plugged on to the controller board.

Certain Way numbers (see under) are allocated as standard to peripheral units, although in systems containing two or more identical peripherals only the first of each type is allocated the standard Way number

| PERIPHERAL                 |           |     | WAY NO.   |   |

|----------------------------|-----------|-----|-----------|---|

| Paper Tape Reader 500      |           |     | 0         |   |

| Paper Tape Punch 110       |           |     | 1         |   |

| Control Teleprinter or The | rmal Prin | ter | 2         |   |

| Line Printer               |           |     | 3         |   |

| Interval Timer             |           |     | 7         |   |

| Cartridge Disc             |           |     | 8 and 9   |   |

| Magnetic Tape              |           |     | 10 and 11 |   |

| H.P.T. Disc                |           |     | 12 and 13 | 3 |

#### NORMAL INTERFACE LOADING

# 4.1 SCOPE

This section explains Normal Interface loading and how transfer priority is accorded to the various peripherals in a system. A straightforward method of allocating Ready numbers, which is applicable, without further verification to lightly loaded systems, is described.

Supplement 2 provides a fuller method of analysing worst-case input/output conditions in which all the peripherals demand simultaneous transfers, to determine whether or not they can be serviced without performance degradation or transfer failure.

# 4.2 GENERAL CONSIDERATIONS

The Basic Multiplexer Channel (BMC) multiplexes and routes data transfers, via the Normal Interface, between store and any of up to 256 peripheral controllers (section 3). To enable this facility to be used without either loss of data or peripheral speed degradation the following rules must be obeyed,

- (a) The peak loading presented by such transfers must not exceed the capacity of the interface, and

- (b) peripheral priority allocation (Ready numbers) must be correctly made so that the transfer demands are satisfactorily interleaved and transfers serviced in time.

Once initiated, each autonomous transfer, whether in single or burst mode, occupies the interface for a period of time defined as the Hold Time (H). H depends on the design of each particular peripheral controller, the design of the channel controller and the length of any links over which the transfer passes.

A peripheral running at its nominal full rate demands transfers over the Normal Interface at intervals whose time duration is defined as its Repetition Time (R). Hence the loading, imposed by a peripheral, on the Normal Interface is given by

$$LOAD = \frac{H}{R} \times 100\%$$

The maximum safe load is limited to approximately 90% because of the interconnection between CPU and BMC requests for store cycles.

Most peripherals only maintain the level of interface load for a limited time, and must then wait for some mechanical operation. For example the lineprinter alternates between transfer phase and print phase. Thus the longer term mean loading may be less than that calculated above, and in certain configurations advantage can be taken of this fact. For the purposes of this section, however, the load is assumed to be continuous.

It should be noted, that to allow for safety margins in any loading calculations, all figures quoted in this manual are worst-case times which include allowances for design tolerances, deskewing etc. Furthermore the figures quoted for communications controllers are based on the shortest character setting in each case:

- (a) Asynchronous: 5 bit character with one start and one stop bit i.e. 7 units.

- (b) Synchronous:- 6 bit character.

At a given data rate these settings give the highest loading factor.

The use of Extension Units and Links imposes restrictions on Ready number allocation, since the Normal Interface Link multiplexes the ready lines on its secondary interface to present a single ready line to the primary interface. A group of peripheral controllers housed in an Extension Unit share a single priority level with respect to other peripheral controllers or Extension Units connected to the primary interface. Thus, for example, if two Peripheral Link units, A and B are allocated Ready numbers 2 and 3 respectively all peripheral controllers on Link A have priority over those on Link B.

# 4.3 SIMPLE RULES FOR INTERFACE LOADING AND READY NUMBER ALLOCATION

Theoretical assessment of a generalised time-sharing mechanism indicates that, for load factors below 60%, the mechanism will always function correctly provided that time-slot allocations for each task are correctly ordered.

For a given GEC 4080 configuration, therefore, provided that the Normal Interface loading does not exceed 60%, the following simple procedure can be employed to allocate Ready numbers to the peripheral controllers. In the event that the loading factor exceeds 60% the interactive procedure given in Supplement 2 must be employed to verify correct operation of the interface or advice sought from GEC Computers Ltd.

#### (a) Determination of Loading

Any peripheral operating at full speed requires a specific percentage of the Normal Interface time to service its autonomous transfers. To determine whether or not a given group of peripherals can operate concurrently at full speed the percentage given in the LOAD column of Table 1 should be added. If this procedure indicates a total loading not exceeding 60%, Ready numbers allocated in the manner indicated in the following paragraphs ensure satisfactory operation.

#### (b) Ready Number Allocation

In 4080 configurations Ready numbers must be in the range 0 to 15. However each Ready number may be further subdivided when peripheral controllers are housed in an extension unit. The peripheral controller's Ready numbers are multiplexed onto one ready line on the link to the CPU. The link may be patched to any Ready number at the CPU.

For ease of reference Ready number notation 2/3 indicates a peripheral controller, with Ready number 3, housed in an Extension Unit which is connected, via a link, to the primary interface at Ready 2 (Table 2).

In principle any Ready number can be allocated to any device as long as the relative priority order is correct. If, as with Way numbers, two Ready numbers are required by a peripheral controller the mandatory rules in the description of the controller must be obeyed.

Configurations whose interface loading does not exceed 60% may have Ready numbers allocated directly in the order of Limiting Times as listed in Table 1. A full description of the term Limiting Times is provided in Supplement 2. Peripheral controllers with the lowest limiting time must be allocated the highest priority level and hence the lowest Ready number.

Table 2 provides a worked example of a typical configuration. The example has been checked using the procedure in Supplement 2 and the column headed ORDER refers to the results of priority allocation based on this procedure.

TABLE 1

PERCENTAGE LOADS AND LIMITING TIMES

| PERIPHERAL          |                             | % LOAD | LIMITING<br>TIME ( <sub>j</sub> us) |

|---------------------|-----------------------------|--------|-------------------------------------|

| HPT Disc            | 1:1 Interlace 16 bit N.I    | 69     | 34.0                                |

|                     | 1:2 Interlace 16 bit N.I    | 34     | 68.8                                |

|                     | 1:3 Interlace 16 bit N.I    | 23     | 103                                 |

|                     | 16 bit N.I                  |        |                                     |

| Cartridge Disc      | 1:1 Interlace 16 bit N.I    | 38.2   | 65                                  |

|                     | 1:2 Interlace 16 bit N.I    | 19.1   | 130                                 |

|                     | 1:3 Interlace 16 bit N.I    | 12.7   | 195                                 |

|                     |                             |        |                                     |

| Magnetic Tape Syst  | tem (30K)                   | 11.9   | 130                                 |

| Paper Tape Reader   |                             | 0.55   | 400                                 |

| Line Printer (600/  |                             | 1.9    | 880                                 |

| Control Teleprinter |                             | 0.008  | 4500                                |

| Card Reader         |                             | 0.5    | 1200                                |

| Paper Tape Punch    | (110)                       | 0.12   | 8000                                |

|                     | errupting every 1mS)        | 0.6    | 1000                                |

| Watch Dog and Int   |                             | 0.0006 | 100,000                             |

| Asynchronous Hal    | Duplex (7 unit character)   |        |                                     |

|                     | 600 baud                    | 0.07   | 11600                               |

|                     | 1200 baud                   | 0.13   | 5800                                |

| •                   | 9600 baud                   | 1.09   | 730                                 |

| Synchronous Half    | Duplex (6 unit character)   |        |                                     |

|                     | 2400 baud                   | 0.31   | 2500                                |

|                     | 4800 baud                   | 0.62   | 1250                                |

|                     | 48K baud                    | 6.2    | 125                                 |

| Multichannel Asv    | nchronous (7 unit character | ,      |                                     |

| 16 channel 600 b    |                             | 1,44   | 11600                               |

|                     | aud each channel            | 2.88   | 11600                               |

TABLE 2

TYPICAL SYSTEM CONFIGURATION (FIG. 4)

| PERIPHERAL                                           | CONNECTED TO CPU/EXTENSION UNIT | READY NO | ORDER |  |

|------------------------------------------------------|---------------------------------|----------|-------|--|

| Paper Tape Punch (110)                               | CPU                             | 5        | 4     |  |

| Paper Tape Reader (500)                              | CPU                             | 1        | 3     |  |

| Teleprinter ASR33                                    | CPU                             | 4        | 4     |  |

| Interval Timer                                       | CPU                             | 2        | 3     |  |

| Line Printer (600)                                   | EU                              | 0/3      | 3     |  |

| Card Reader (400)                                    | EU                              | 0/4      | 3     |  |

| Sync Modem I/F (6 unit, 48K baud)                    | EU                              | 0/1      | 9     |  |

| Mag. Tape System                                     | EU                              | 0/2      | 2     |  |

| Cartridge Disc (1:1 Interlace)                       | EU                              | 0/0      | 1 7   |  |

| 32 Async Multichannel I/F (7 unit<br>2.4K baud each) | EU                              | 3/0      | 4     |  |

The Normal Interface loading of this configuration is approximately 71% A configuration comprising any sub-set (or the whole) of that shown in Table 2 need not have the loading rules applied, providing that the Ready numbers allocated retain the relative priority sequence shown in Table 2, the actual value of the Ready number not being significant. If no specific reason exists for choosing particular number to form the sequence, the actual numbers given in the Ready No. column of Table 2 should be used for the sake of consistency.

# **SLOT ALLOCATION RULES**

These rules must be obeyed when system configurations are specified. They arise from consideration of board position and power supply current. The mechanical requirements for the various peripheral controllers are:

| Peripheral Controller       | Slots Required |

|-----------------------------|----------------|

| Interval Timer              | 1              |

| Magnetic Tape               | 2              |

| Card Reader                 | 1              |

| Cartridge Disc              | 2              |

| Head per Track Disc         | 3              |

| Paper Tape Reader (500)     | · 1            |

| Paper Tape Punch (110)      | 1              |

| Control Teleprinter         | 1              |

| Line Printer                | 1              |

| Watchdog and Interrupt Unit | 1              |

| Modem Interface             |                |

| (Single Channel Synchronous | 1 .            |

| or Asynchronous)            | 1              |

| 16 Channel Modem Interface  | 4              |

| 32 Channel Modern Interface | 5              |

|                             |                |

The 16 and 32 channel controllers must be housed in the EMC or Extension Unit.

Each store link occupies one slot in CPU or IOP as appropriate.

Each Normal Interface link occupies one slot in each of the two units linked.

# 5.1 CENTRAL PROCESSOR

5

The Central Processor Unit is slot, rather than power supply limited. A total of 9 slots are available for store links, peripheral links and peripheral controller boards.

# 5.2 EXTENSION UNIT

An Extension Unit is connected to a superior Normal Interface by a Peripheral link (Supplement 1) which requires one board position (slot) in the Extension unit. Each Extension Unit contains a further 13 slots. However, the total number of slots that may be used assuming averaged power consumption figures for peripheral controllers is limited by the maximum specified ambient temperature in which the unit has to operate. This relationship is shown as follows:

| Temperature       | Slots |

|-------------------|-------|

| 55 <sup>O</sup> C | 8     |

| 50°C              | 9     |

| 45 <sup>0</sup> C | 10    |

| 40°C              | 11    |

13

Thus any Extension Unit which is never subject to temperatures exceeding 40°C may contain a total of 11 boards of which 10 may be peripheral controllers.

Multi channel communication controllers take up to 50% greater power per board than average. Hence for power calculation purposes they consume 50% more slot power. In critical cases advice should be sought from G.E.C. Computers Ltd.

# 5.3 BOARD POSITIONING

| 25                            | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | <u> </u>                         |

|-------------------------------|----|----|----|----|----|----|----|----|----|----------------------------------|

| INTERFACE<br>TERMINATION UNIT |    |    |    |    |    |    |    |    |    | CENTRAL PROCESSOR UNIT<br>BOARDS |

SLOT POSITIONS WITHIN CPU

#### Rules

- (a) Slot 25 is reserved for the Interface Termination Unit

- (b) Multiple board controllers, such as a disc controller, which require a link on EC2 can only be fitted into slots 21 to 24

- (c) Store interface link boards are fitted to slots 16 to 19.

(d) Normal Interface peripheral controller boards and Normal Interface link boards are fitted to unused slots 16 to 24 starting with the lowest available number.

| 15        | 14  | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | , 5 | 4 | 3    | 2        | 1        |     | <u></u>         |

|-----------|-----|----|----|----|----|---|---|---|---|-----|---|------|----------|----------|-----|-----------------|

|           | N 7 |    |    |    |    |   |   |   |   |     |   |      |          |          |     |                 |

| H N       |     |    |    |    |    |   |   |   |   |     |   |      |          |          |     |                 |

| INTERFACE |     |    |    |    |    |   |   |   |   |     |   |      |          |          | 1 . | POWER<br>SUPPLY |

| INTE      |     |    |    |    |    |   |   |   |   |     |   |      |          |          |     | UNIT            |

| TERA      |     | ٠  |    |    |    |   |   |   | - | W.  |   |      |          |          |     |                 |

|           |     |    |    |    |    |   |   |   |   |     |   | ليسا | <u> </u> | <u> </u> |     |                 |

# **EXTENSION UNIT RACK**

#### Rules

- (a) Slot 15 is reserved for the Interface Termination Unit

- (b) The Peripheral Adaptor board, that board connected to a superior Normal Interface, must occupy slot 1, and in a switched extension unit the second peripheral adaptor board must occupy slot 2.

- (c) Multiple board controllers may be fitted in any position. One board is connected to the Normal Interface, the other boards occupying the slots to the left.

- (d) Channel adaptor boards connected to further inferior Normal Interfaces, and peripheral controller boards should preferably be located starting from the lowest numbered and available slot.

6

# OVERLOAD EFFECTS

This section of the manual summarises the effects, on peripheral equipment, of an overload on the Normal Interface i.e. if the Limiting Time (TL) for a peripheral is exceeded.

# 6.1 INTERVAL TIMER

An overload will result in loss of transfer and system action is liable to delay. Losses may be detected by use of the Interrupt Count Facility. Software recovery is necessary.

# 6.2 MAGNETIC TAPE CONTROLLER

A status report at the end of block will indicate transfer failure. Software recovery is necessary by Backspace followed by re-read or re-write as appropriate.

# 6.3 CARD READER CONTROLLER

A status report is given in the end of the read operation and the Reader stops. Manual re-insertion of the card is necessary.

# 6.4 CARTRIDGE AND HPT DISCS

Full sector buffering is provided in the controller, and if the filling or emptying of the buffer is momentarily slowed during a read or write operation on the disc, a complete disc revolution may be lost, depending on the state of the buffer. Recovery by re-reading or re-writing on the next revolution is automatically attempted by the controller. On a HPT disc unit a status indication is given.

# 6.5 PAPER TAPE READER (500) AND PUNCH (110)

An overload causes the transfer rate for both these units to slow down.

# 6.6 TELEPRINTER CONTROLLER (ASR33)

(a) Read from Keyboard

A transfer failure occurs, and a status report is given. Recovery action is by software and manual intervention.

(b) Read from Paper Tape and Write to Printer/Punch

Overload causes the transfer rate to slow down in both instances.

# 6.7 LINE PRINTER (300/136 and 600/136)

A delay in filling the Line Printer buffer causes an appropriate delay in the start of print-out and the printing rate is slowed.

# 6.8 WATCHDOG AND INTERRUPT UNIT

If the unit is in the CPU Primed mode it initiates an alarm unless the CPU performs a transfer to Watchdog every 15  $^{\frac{1}{2}}$  10%. In the Interrupt mode the unit initiates an alarm unless the interrupt is acknowledged within 100mS.

Interrupts are latched and wait for service .Hence further interrupts on the same line which occur during the waiting period will be missed if the period is extended because of an overload.

# 6.9 MODEM INTERFACES

In the receive mode if transfer failure occurs, the recovery action depends on the system in question. In general recovery demands re-transmission of the message and hence is lengthy. In the transmit mode the transfer rate is slowed. Synchronous controllers insert a SYN character, which may represent a message failure depending upon the protocol in use. In all instances, a status report of such an occurrence is given at the end of the block transfer.

# Supplement 1: LIST OF UNITS

- 1. 4080 Central Processor, Power Supply and Initial Program Load assembly

- 2. 4080 Core Store, Power Supply and Store Link

- 3. Extension Units and Normal Interface Links

- 4. Interval Timer

- 5. Watchdog and Interrupt Unit

- 6. Teleprinter

- 7. Reader 500

- 8. Punch 110

- 9. Cartridge Disc

- 10. Magnetic Tape 30 KHz

- 11. Line Printer 300/80, 300/136, 600/136

- 12. Single Channel Modem Interface Controller Asynchronous

- 13. Single Channel Modem Interface Controller Synchronous

- 14. Multichannel Modem Interface Controller Asynchronous

- 15. Card Reader

- 16. Thermal Printer

- 17. Cyclic Redundancy Checking Unit

- 18. Teleprinter Compatible Display

- 19. Simple Graphics Display

- 20. Visual Display Terminal

- 21. External Multiplexer Channel

- 22. Dot Matrix Printer

# 4080 CENTRAL PROCESSOR, POWER SUPPLY AND INITIAL PROGRAM LOADER ASSEMBLY

The Central Processor Unit (CPU) is the fundamental unit of a GEC 4080 system. The CPU comprises three major electronic sub-assemblies, a Central Processor (CP) which provides the arithmetic and logic capability of the system, a Basic Multiplexer Channel (BMC) which provides the basic Input/Output capability of the system and a Control and Monitor Unit (CMU) by means of which both the CP and BMC are controlled, and which also provides wide ranging maintenance facilities.

The CP comprises eleven logic boards, the BMC three logic boards and the CMU a single logic board plus a panel of lamps and switches which forms the front panel of the CPU. The CPU provides positions for twenty-five logic boards of which fifteen are allocated for the CP, BMC and CMU, and one for an Interface highway termination board the remaining nine board positions being available for units such as Store Interface Links or Peripheral Controllers.

The top third of the 12% ins. high CPU front panel is formed by a grill and filter through which air is drawn by cooling fans mounted on the rear face of the unit.

Initial Program Load (IPL) for a GEC 4080 system is acheived by loading a short program into store and subsequently acting upon the program. This program is held in Read Only Memories (ROMs) mounted on an Initial Program Logic Assembly, (IPLA) and its function will normally be to load systems software into store via a predefined peripheral device. The CPU provides for the fitting of two independent IPLA's, hence IPL can be performed from either of two peripheral devices. The IPLA's are located on the top edge connector of the Arithmetic board of the CP.

Three IPLA's are available; others may be added later -

# IPLA Type 11

This provides for IPL from either a Paper Tape Reader 500 or the reader of a teleprinter

# IPLA Type 12

This provides for IPL from a specially prepared file on a Magnetic Tape Handler.

# IPLA Type 14

This provides IPL from a specially prepared file on a Head Per Track or Cartridge Disc Mechanism.

#### **POWER SUPPLY**

The Power Supply Unit (PSU) provides the DC power required by the CPU

The DC supplies provided by the PSU are sequenced, to ensure that system integrity is maintained, whilst the supply is switched on and off.

Power is supplied to the CPU by means of cables anchored at the processor and and terminated at the PSU end by plugs and sockets. The PSU is cooled by fans mounted on its rear face; cooling air is drawn through a grill and filter on its front face and expelled at the rear.

# **OPERATIONAL CHARACTERISTICS**

#### **Formats**

The CPU provides an extensive repertoire of instructions for arithmetic and logical operations on single bit, 8 bit (byte), 16 bit, and 32 bit data. Floating Point instructions are provided as standard, using 32 bit and 64 bit floating point number formats.

#### **Performance**

The CP is provided with extensive hardware support for multiprogrammed operation. In particular, store protection is provided by means of 4 hardware segment (Base and Range) registers whilst other aspects are handled by the hardware Nucleus.

The Nucleus provides a number of functions normally performed by a Software Executive. These include: -

Maintaining protection between programs

Providing communications facilities between programs

Short term scheduling of programs

Providing fully protected Input/Ouput facilities

Routing of interrupts to appropriate programs.

The communication feature is based on the use of messages passed between Co-routines; Semaphore claim and release operations are also provided to facilitate communication via shared data areas.

The CP has error handling capability; allowing the immediate action which may be necessary to prevent the effects of the error from propagating through the system. Upon error detection the Nucleus will form an error message and cause a reschedule operation to select an Owner or Error Process to run to deal with the error. The message contains an error code indicating the nature of the fault e.g. store parity failure, power failure, protection violation.

The CMU provides facilities for the Control of the CP and BMC, and facilities for the monitoring of registers and data highways within the CP and BMC for maintenance purposes. The front panel of the CMU provides:

- (a) Two rows of lamps on which register contents and data highways may be displayed. The information displayed is selected by 4 rotary switches.

- (b) One row of data switches. Data patterns set up on the switches may be written into hardware registers by operation of CMU controls, and may also be read, for engineering purposes, by programmed instructions.

- (c) Control switches and Indicator lamps. The control switches perform such functions as Reset/Run/Initial Program Load whilst the indicators display the CPU run state.

#### Interface

The BMC performs data transfers between I/O devices (such as peripherals and communications units) and main storage. Transfers of data are carried out via a standardised interface, called the Normal Interface; such transfers are carried out autonomously by the BMC in parallel with CP activity.

The Normal Interface provided by the BMC is a superset of that provided by the GEC 2050, differing only in the width of the Information highway: 16 bits are available with the 4080 BMC whilst the GEC 2050 provides only 8 bits of Information.

# Summary of Operational Characteristics

CP :- Instruction Length Instruction Repertoire Program Accessible Registers 16 bits 180 Approx. including Floating Point 8

# **Arithmetic and Logical Operations**

Logical, 1 bit operands arithmetic & Logical, 8 bit operands arithmetic & logical, 16 bit operands arithmetic & logical, 32 bit operands Floating Point, 32 & 64 bit numbers

Main Store Capacity

Store Protection

Multiprogramming Hardware

32Kb - 256Kb

4 Hardware Segment Registers

Microprogram Nucleus providing

Protection, Communication, Scheduling

and Input/Output facilities.

#### BMC:-

Number of READY lines Number of WAYS (= number of simultaneous transfers)

Transfer types

16

256

Autonomous, 1 or 2 byte Autonomous burst mode Programmed, 2 byte

CMU:-

Control facilities

Monitor facilities

Number of points monitored

Store Test facilities

**BMC** test facilities

**CPU** test facilities

Include START, STOP, RESET, IPL 39 data lamps + 18 data switches Approx. 1400 logic signals Read or Write to store from CMU switches and lamps Initiate Autonomous transfer by manual operation of CMU Obey instruction from data switches, take operand from data switches.

Micro step and Instruction step

# Typical Operations Times (microseconds)

| ADD                   | and the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.1           |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| MULTIPLY 16 x 16      | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3.6           |

| 16 x 32               | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.85          |

| <b>DIVIDE</b> 32 ÷ 16 | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20.35         |

| BRANCH                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.35          |

| SHIFT (N bits)        | and the second s | 2.3 + 0.5N    |

| BYTE STRING MANIP     | ULATION (N bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1.55 + 2.35N  |

| REGISTER TO REGIST    | TER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2.35          |

| F.Pt. ADD             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.8           |

| MULTIPLY              | 32 bit Operands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>⋠ 10.9</b> |

| DIVIDE                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19.4          |

The above are based upon a nominal store cycle of 550 nanosecs.

The full set of Instruction times are given in the Performance Manual.

# **ELECTRICAL CHARACTERISTICS**

# D.C. Requirements

The seperate PSU provides for the CPU

+5 volts 70 amps +15 volts 1.5 amps -15 volts 1.5 amps - 5 volts 5.0 amps

# A.C. Requirements

Voltage - The nominal supply voltage to the Power Supply is preset to 200, 220v, 230v, 240v or 250v single phase by transformer tap selection.

Voltage variation - 10%

Frequency - 48 - 66 Hz

Consumption - 1.0 KVA

Break Duration - Half cycle dropout.

In the event of a mains failure, the PSU down sequences the d.c. supplies in a prescribed order, and with sufficient time, for the processor to take the necessary action to avoid corruption of the program.

# **Power Control**

Power is controlled via the ON/OFF switch located on the Central Processor control panel.

#### **Protection**

The Power Supply embodies protection against under voltage, over voltage and over current of the d.c. output supplies. Protection is also provide against over temperature of both the Power Supply and the Central Processor.

Main storage for a 4080 system is provided by modules of 2½D core store. The modules currently available are:-

# Core Store, 32K Byte

This is a 19" rack mounting unit providing 32Kb of storage. Data may be written and read as 8 bit bytes or 16 bit halfwords. During a write operation parity bits are formed for each byte written, and during a read operation the parity of each byte read is checked. Parity failures are signalled to the Central Processor Unit (CPU), and are also indicated by a lamp on the front of the unit.

The unit includes a Store Access Director (SAD) which provides for the CPU and up to 3 Input/Output processors to be connected to the unit, via Store Interface Links.

# Core Store, 64K Byte

This is similar to the 32K Store except that the unit provides 64 Kb of storage.

# Core Store Expansion Unit, 32K Byte

This unit is provided to allow field expansion of the 32K byte Core Store, to provide a total of 64 Kb of core storage.

# The Power Supply, Store

This 5½" high 19" rack mounting unit provides DC power for one 32/64KB store module. The unit contains sequencing logic necessary for retaining store contents with mains failure.

Power is supplied to the store by means of cables anchored at the store end and terminated at the Power Supply end by plugs and sockets. The unit is force air cooled by fans mounted on its rear face; cooling air is drawn through a grill and filter on its front face and expelled at the rear.

# The Store Link

It consists of a Store Link board which is plugged into a free board position in the processor, a Store Port board which is plugged into a free board position in the store module, and a pair of lightweight cables connecting the two boards. The maximum cable length is 10 ft.

# **OPERATIONAL CHARACTERISTICS**

#### **Formats**

Store Width

16 bits + 2 parity

Module sizes

32 and 64 kilobytes

#### Performance

2½D ferrite core system having a nominal store cycle time of 550 nanoseconds.

# A.C. Requirements

Voltage - The nominal supply voltage to the Power Supply is preset to 200, 220v, 230v, 240v or 250v single phase by transformer tap selection.

Voltage variation ± 10%

Frequency - 48 - 66 Hz

Consumption - 1.0 KVA

Break Duration - Half cycle dropout.

In the event of a mains failure, the PSU down sequences the d.c. supplies in a prescribed order, and with sufficient time, for the processor to take the necessary action to avoid corruption of the program.

# **Power Control**

Power for a 4080 system is controlled via the ON/OFF switch located on the CPU front panel. A local ON/OFF switch is provided on the PSU rear panel.

#### **Protection**

The Power Supply embodies protection against under voltage, over voltage and over current of the d.c. output supplies. Protection is also provided against over temperature of both the Power Supply and the Core Store.

The extension unit is available to supplement the slots provided in the 4080 CPU for peripheral controllers. It may be used with any input/output processor which generates a normal interface.

Extension units are connected to the associated processor by means of a link. On 4080 systems this is usually either the single or two byte peripheral link. The link generates a secondary normal interface in the extension unit. The peripheral link is a multiplexing link, that is to say it multiplexes 16 Ready lines on the secondary normal interface, and uses one Ready line on the primary normal interface.

#### **Extension Units**

The number of peripheral controller and link boards that may be fitted is limited by the rated capacity of the power supply.

The use of switchable extension units and multiple links in multicomputer systems enables groups of peripheral controllers to be switched between the various processors. Switchable extension units may be controlled by either a local key operated rotary switch, or by a user supplied remote switching equipment, dependent on the system requirements.

# Peripheral Links

A peripheral link consists of three sections

- (i) A channel adaptor board which plugs into the primary Normal Interface backplane

- (ii) A peripheral adaptor board which plugs into the secondary Normal Interface backplane

- (iii) One or two interconnecting cables. One cable carries the various control signals and the less significant byte of data. The second cable is only used for the 2 byte link, and carries the more significant byte of data.

There are two versions of peripheral adaptor board the standard and the type B. They differ in that the type B board does not contain any terminating resistors for the secondary Normal Interface.

Single links between a processor and an extension unit use a standard peripheral adaptor board. If there are multiple links between several processors and a switchable extension unit then one of the peripheral adaptor boards will be a Standard one, the remainder will be type B. In either case the interconnecting cables may be up to 30 metres long.

# **External Interface**

The External Interface is provided to enable a user to connect his equipment to the Normal Interface without mounting it in a GEC Computers Ltd rack. This interface consists of a channel adaptor board and either one or two interconnecting cables as required.

# Way and Ready Numbers

The links do not use a Way number, they have one Ready number on the primary Normal Interface.

This unit is designed to generate interrupts to the Central Processor, the time interval between interrupts being controlled by software. The unit facilitates the maintenance by software of a Time of Day clock, as well as other timer facilities required for Real Time software.

The Timer comprises a single board of logic, which occupies a Normal Interface board position in the Central Processor shelf.

#### Formats

Time interval settings

250 Jusec min.

to 1.02375 sec max.

in

250 usec steps.

# Performance

Long Term stability

less than 1 sec.

drift in 24 hours.

# Interface

The Timer uses the 16 bit Normal Interface.

# Way and Ready Numbers

The interval timer uses one Way and one Ready number.

The Watchdog and Interrupt unit provides a means of monitoring the operation of the computer and also a means of routing signals from external equipment into the processor as interrupts. It is physically divided into two sections, a printed circuit logic board and a signal distribution unit.

# Watchdog Unit

The Watchdog unit generates an alarm signal if it does not receive a program output transfer from the processor at a pre-specified time. The alarm signal may be used to activate a user supplied alarm.

Two main modes of operation are available. In one mode the Watchdog unit generates an alarm if it receives a program output transfer at any time except the period between 900 and 1100 milliseconds after the preceding program output transfer. In the second mode the Watchdog unit generates interrupts at one second intervals, and generates an alarm if a program output transfer is received at any time except for the 100 millisecond period after the interrupt has been generated.

The alarm state causes a pair of relay contacts to open. These contacts are available at the signal distribution unit.

# **External Interrupt Unit**

The Interrupt Unit monitors the state of four pairs of lines, connected to it via the signal distribution unit. Whenever one of the lines changes state, in a pre-specified direction, then an interrupt is generated to the CPU.

The direction of change which causes the interrupt is pre-specified under program control. The unit contains logic to ignore contact bounce and signal oscillations on the line, after an interrupt has been initiated. This blanking period can be either 32 milliseconds (e.g. for relay generated signals) or 320 u seconds (e.g. for logic driven signals) as determined by hardware patches.

#### Signal Distribution Unit

This small unit is generally mounted in the rear of the cabinet and contains five sockets with mating plugs which enable user supplied equipment to be connected to the alarm lines and interrupt signal lines.

# Way and Ready Numbers

The Watchdog and Interrupt unit uses two consecutive Way Numbers. If both facilities are used then the even Way number applies to the Watchdog, and the odd Way number to the Interrupt unit. If only one facility is required then it can use any Way number. The unit uses one Ready number.

# TELEPRINTER

The Control Teleprinter provides a hard copy or paper tape output from the computer and permits messages to be input from either the keyboard or the integral paper tape reader.

The Control Teleprinter peripheral comprises a controller (which occupies one Normal Interface slot), a signal cable, a mains cable, and teleprinter mechanism.

Various versions of the mechanism are available i.e.

ASR33

DD390 (lo

(low noise version of ASR33)

All are complete with a floor stand.

The controller transfers data across the Normal Interface in 8 bit bytes. There are two modes of data transfer

(a) Binary Mode

The eight data bits are transferred directly to the teleprinter/controller interface on output ( or vice-versa on input).

(b) Character Mode

The least significant seven bits are transferred as in Binary mode. The eighth bit is set to form overall even parity on output. On input the eighth bit is checked for even parity.

#### Performance

**Keyboard Printer**

Maximum speed

10 characters/sec (nominal)

Character set

ISO-7- UK (64 character subset)

Printer Column width

72 characters

Paper width

216 mm (8½ in.).

Paper tape Punch & Reader

Paper tape width

25.4 mm (1 in.)

Number of channels

8

Speed

10 characters/sec.

# Interface

The 8 bit Normal Interface is used, data being transferred by autonomous input/output cycles. Burst mode is not used.

# Way and Ready Numbers

The Teleprinter controller uses one Way and one Ready number.

The Paper Tape Reader 500, is a paper tape input peripheral capable of reading at a maximum speed of 500 characters per second. The mechanism uses a dielectric reading principle.

The reader controller is built on one standard printed circuit board. This board plugs into any Normal Interface peripheral slot, and controls one reader mechanism.

The reader mechanism with tape dispenser is mounted in the rack mounting equipment which fits a standard 19" rack.

An interconnecting cable joins a connector on the controller board with a connector on the rack mounting equipment.

#### **Formats**

The reader controller transfers data in 8 bit bytes from the reader mechanism to the Normal Interface.

There are two modes of data transfer:

(a) Binary Mode

In this mode track 8 is transferred to the Normal Interface.

(b) Character Mode

In this mode track 8 is transferred to the Normal Interface as an 'O' and the controller checks even parity on the paper tape.

# Performance

Reader Speed Nominal

500 characters/sec.

Tape

1" 8 hole Paper Tape or any Plastic Tape (not metallised)

punched to BS.3880

Form

Coiled only.

Reader dispenser capacity

5" diameter coils.

#### Interface

The 8 bit Normal Interface is used, data being transferred by autonomous input cycles. Burst mode is not used.

# Way and Ready Number

The Paper Tape Reader Controller uses one Way and one Ready number.

The Paper Tape Punch 110 is a paper tape output peripheral capable of punching at a maximum speed of 110 Characters per second.

The punch controller is built onto one standard printed circuit board. This board plugs into any Normal Interface peripheral slot and controls one punch mechanism.

The Paper Tape Punch mechanism is 19 inch rack mounting.

The inter-connecting cable joins an edge connector on the punch controller board with a connector on the punch mechanism.

# **OPERATIONAL CHARACTERISTICS**

#### **Formats**

The punch controller transfers data in 8 bit bytes from the Normal Interface to the punch mechanism. There are two modes of data transfer:

- (a) Binary Mode In this mode track 8 corresponds to the Normal Interface.

- (b) Character Mode In this mode track 8 does not correspond to the Normal Interface, but is set to maintain even parity over each 8 bit byte on the paper tape.

#### **Performance**

**Punch speed Nominal**

110 Characters/sec.

Tape

1 inch 8 hole paper tape. Punched to BS. 3880