# User Hardware Handbook INTERFACES

# C GEC Computers Limited 1977

The information presented herein is, to the best of our knowledge, true and accurate. No warranty or guarantee, expressed or implied, is made regarding the accuracy of information supplied or capacity, performance or suitability of any product or service since the manner of use is beyond our control.

You are advised that you should ensure that the information contained herein has not been superseded.

All our products, materials and services are sold subject to our Conditions of Sale, available on request.

GEC COMPUTERS LIMITED

Elstree Way, Borehamwood, Hertfordshire.

Telephone No. 01-953-2030

Holding Company - the General Electric Company Limited of England

# **INTERFACES**

# CONTENTS

|    |      |                        |        |        |        |       |                 |     |      |           |      |     | Page |

|----|------|------------------------|--------|--------|--------|-------|-----------------|-----|------|-----------|------|-----|------|

| 1. | INTR | ODUCTION               |        |        |        |       |                 |     |      |           |      |     |      |

|    | 1.1  | Types of Interface     |        | •••    | •••    | , ••• | 71 T <b>444</b> | ••• | •••  | <b>**</b> | •••  | ••• | . 1  |

| 2. | SYST | EM ASPECTS             |        |        |        |       |                 |     |      |           |      |     |      |

|    | 2.1  | Internal Interfaces    | •••    | •••    | •••    | •     | •••             | ••• |      | •••       | •••  |     | 2    |

|    | 2.2  | External Interfaces    | •••    | •••    |        | •••   | •••             | ••• | •••  | •••       | •••  | ••• | 2    |

| 3. | NOR  | MAL INTERFACE          |        |        |        |       |                 |     | •    |           |      |     |      |

|    | 3.1  | General Information    | •••    | •••    |        | •••   | •••             | ••• | •••  |           | ** * | ••• | 4    |

|    | 3.2  | Interface Operation    | •••    | •••    |        | •••   | •••             | ••• | •••  | • •••     | •••  | ••• | 4    |

|    | 3.3  | Physical Interface Con | nectio | ons ar | nd Sig | nals  | •••             |     |      | •••       |      | ••• | 22   |

| 4. | EXTE | RNAL LINK              |        | *      |        |       |                 |     |      |           |      |     |      |

|    | 4.1  | General Information    | •••    |        |        | •••   | •••             | ••• | •••  | •••       | •••  | * . | 26   |

|    | 4.2  | Logical Operation      |        | •••    |        |       | •••             | ••• |      | •••       | •••  | ••• | 26   |

|    | 4.3  | Implementation         | •••    | •••    | •••    | •••   | •••             | ••• |      | •••       | •••  | ••• | 27   |

| 5. | EXTE | RNAL STORE INTERFA     | ACE    |        |        |       |                 |     |      |           |      |     |      |

|    | 5.1. | General Information    |        | •••    | •••    | •••   | ***             | ••• | •••  |           |      |     | 31   |

|    | 5.2  | System Aspects         | • •••  | •••    | •••    | •••   | •••             | ••• |      | •••       | •••  | ••• | 31   |

|    | 5.3  | Interface Operation    | · · ·  |        | •••    |       | •               |     | **** | •••       | •••  | ••• | 34   |

|    | 5.4  | Method of Connection   |        | •••    |        | •••   | •••             | *** | •••  | •••       | •••  | ••• | 42   |

| 6. | СОММ | AND INTERFACE          |        |        |        |       |                 |     |      |           |      |     |      |

|    | 6.1  | System Aspects         | ·      | •••    |        | •••   | •••             | ••• | •••  | ***       |      | ••• | 45   |

|    | 6.2  | Operation              | •••    |        | •••    | •••   | •••             | ••• | •••  | •••       | •••  | ••• | 45   |

|    | 6.3  | Logical Implementation | n .    | •••    | •••    | •••   | •••             | ••• | •••  |           | •••  |     | 50   |

|            | TABLES                                                |    |

|------------|-------------------------------------------------------|----|

| Table 1:   | Cycle Sequence                                        | 10 |

| Table 2:   | Autonomous Cycles                                     | 15 |

| Table 3:   | Program Cycles                                        | 16 |

| Table 4:   | NI Logic Level Connections                            | 24 |

| Table 5:   | Channel Adaptor Board Cable Connections               | 30 |

| Table 6:   | External Store Interface Pin Allocation               | 44 |

| Table 7:   | Command Interface Pin Allocation                      | 52 |

|            | IN-TEXT FIGURES                                       |    |

| Figure 1:  | A Possible System Interconnection                     | 5  |

| Figure 2:  | Unit Heirarchy                                        | 13 |

| Figure 3:  | Operand Subcycle Mode Meanings                        | 17 |

| Figure 4:  | Autonomous/Program Cycle Timing — Single Operand Mode | 18 |

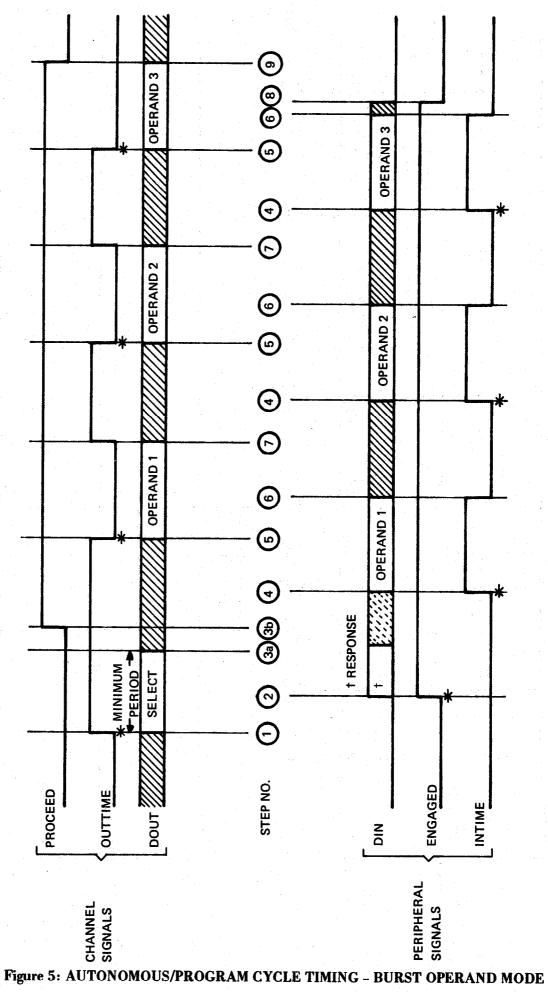

| Figure 5:  | Autonomous/Program Cycle Timing — Burst Operand Mode  | 19 |

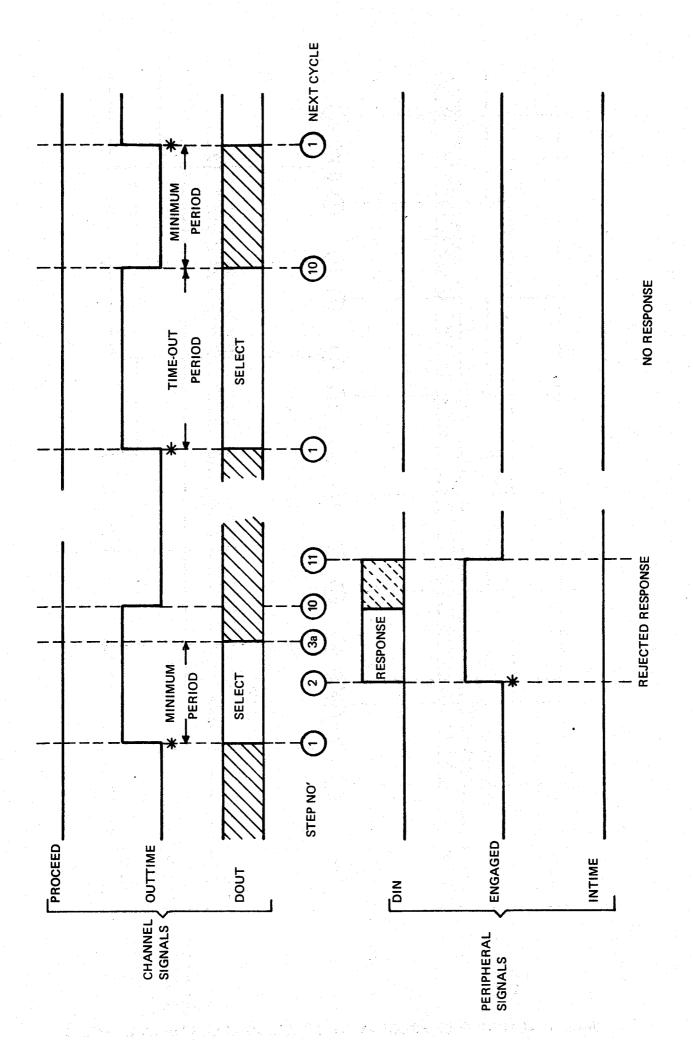

| Figure 6:  | Autonomous/Program Cycle Timing — Abnormal Conditions | 20 |

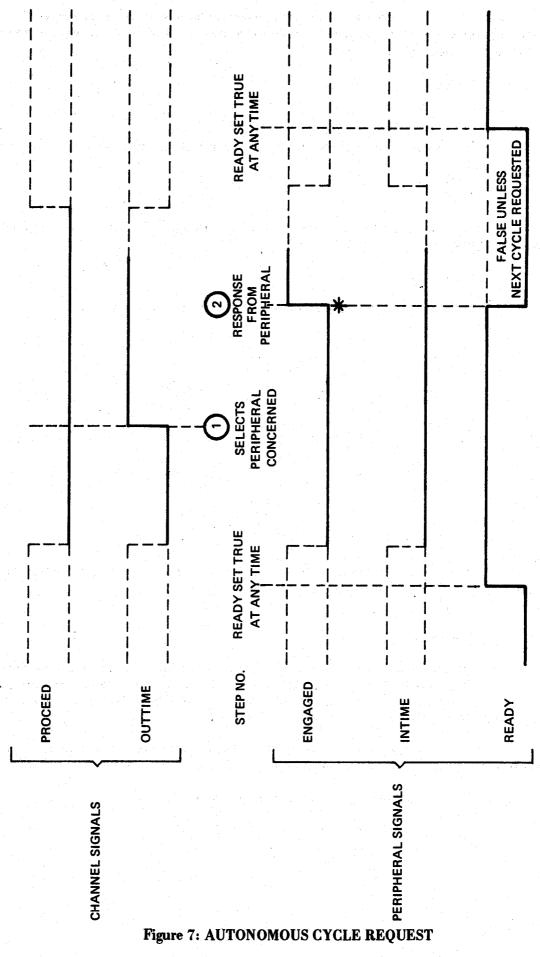

| Figure 7:  | Autonomous Cycle Request                              | 21 |

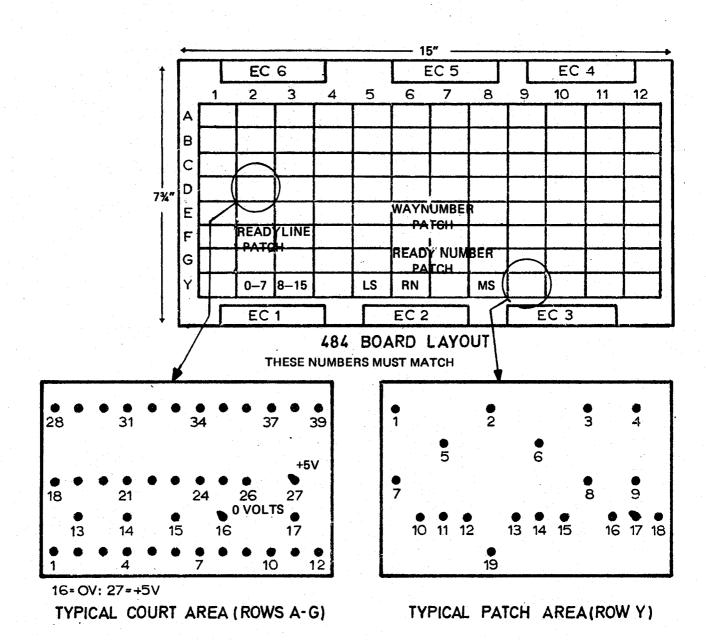

| Figure 8:  | Standard Logic Board                                  | 23 |

| Figure 9:  | Address Part-Cycle Timing                             | 35 |

| Figure 10: | Data Part-Cycle Timing                                | 37 |

| Figure 11: | Relative Timing of Address and Data Part Cycles       | 39 |

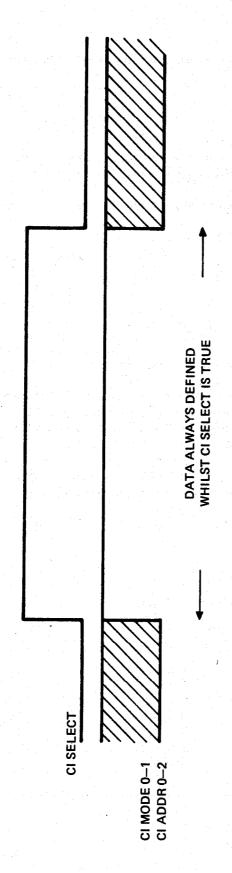

| Figure 12: | Select-Data Timing                                    | 46 |

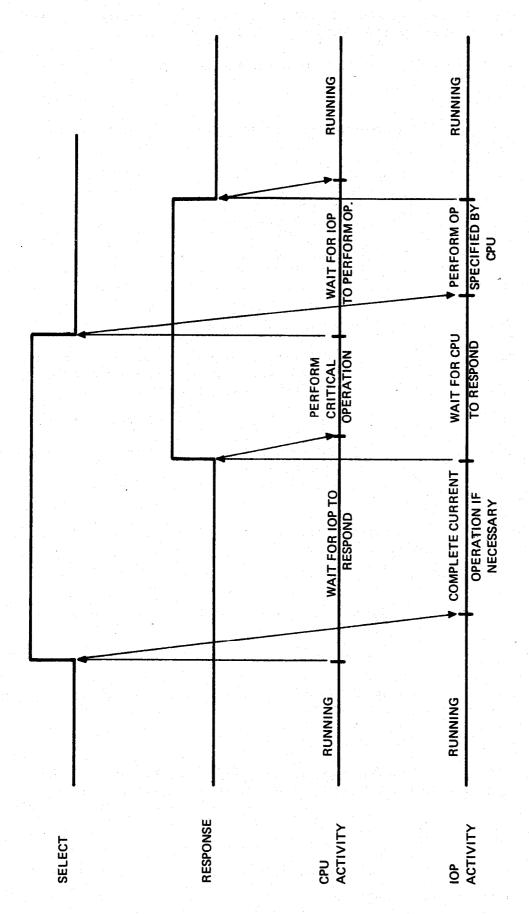

| Figure 13: | Basic Command Interface Cycle                         | 48 |

Page

#### INTRODUCTION

A computer system can contain a number of interfaces of various types across which data can be transferred. These interfaces are defined in this manual to enable a user to select a suitable interface or interfaces for the connection of his own equipment and to design the means of connection. It is intended that this manual provide all the information required; however, any designer with a query is invited to contact GEC Computers Limited.

The interfaces are divided into two categories:-

#### (1) Internal

An internal interface is one within a unit at logic level. The user connects to an internal interface by a plug in board mechanically identical to the standard logic board (See figure 8).

#### (2) External

An external interface is a cable connected to an interface board mounted within a unit.

#### 1.1 TYPES OF INTERFACE

### (a) Normal Interface

The Normal Interface is the interface between a multiplexer channel (such as that situated in the CPU rack known as the Basic Multiplexer Channel) and the peripheral controllers. There are internal and external versions of this interface.

The External Multiplexer Channel (EMC) also provides a Normal Interface and may be used when additional I/O throughput is required to that provided by the BMC.

#### (b) Store Interface

The Store Interface is the interface between a store and any processor (which may be the CPU or an Input/Output processor). There are internal and external versions of this interface, of which, the latter is described in this manual.

#### (c) Asynchronous and Synchronous Serial Interfaces

These external interfaces are used in data communication links often involving the use of Post Office communication facilities.

### (d) Command Interface

This external interface is used by the Central Processor Unit (CPU) to control input/output processors.

#### (e) The Digital Input/Output Interface

The Digital Input/Output Interface is a specially designed simple interface enabling a user to more easily design and attach his own peripheral controller or controllers than if, for example, the Normal Interface was used.

### 2.1 INTERNAL INTERFACES

The Normal Interface is available on the backplane of the CPU. Peripheral controller boards are bus connected to the Normal Interface by plugging the boards into particular slots in the CPU. As the number of slots fed by the bus in the CPU is limited, the Normal Interface can be extended by adding Extension Units. An Extension Unit is connected to the CPU by a Normal Interface link and provides 11 slots into which peripheral controller boards can be plugged for bus connection to the extension (secondary) Normal Interface. A secondary Normal Interface can be extended further by the use of a second Extension Unit connected to the first Extension Unit by another Normal Interface link. However, each extension reduces the maximum rate of data transfer that the interface can achieve. Consequently, a better way of providing extension Normal Interface slots is to link each Extension Unit directly to the CPU.

The Normal Interface as implemented by the BMC can operate at up to 800K bytes per second. An Input/Output Processor IOP, can operate the Normal Interface at up to 2M bytes per second. For the majority of connections which a user may wish to make to a system, the Normal Interface is adequate. For some applications, it may be necessary to connect directly to the Store Interface. This provides a high data rate of up to 2.5M bytes, per second (3.6 Mb = 4080) dependent on the peripheral controller design.

### 2.2 EXTERNAL INTERFACES

The external interfaces available for the connection of user supplied peripherals are:-

### **Modem Interface Asynchronous**

The Asynchronous Modem Interface controller enables Modems or peripherals with the Modem interface to be connected to the CPU via the Normal Interface. Maximum data rate is 9600 baud. Refer to peripheral section of handbook for full details of operation.

#### **Modem Interface Synchronous**

This enables a higher data rate (48K baud) than the Asynchronous Modem Interface. Refer to peripheral section of handbook for full details of operation.

#### **Digital Input/Output**

The Digital I/O controller enables single peripherals to be connected to the CPU via the Normal Interface. It enables easy connection of simple peripherals. The maximum data rate is 200Kbytes/sec, the actual achievable rate depends on the peripheral controller design. Refer to peripheral section of handbook for full details of operation.

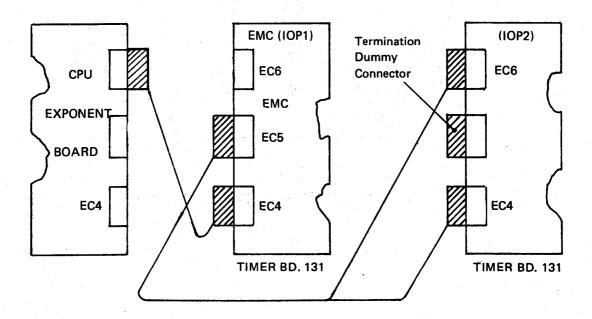

### External Link - Normal Interface

A user may connect directly to the Normal Interface via an External Link. The Channel Adaptor board plugs into a CPU or Extension Unit to pick-up the logic level Normal Interface. The user may connect directly to EC4 and EC6 edge connectors on the board. The maximum cable length is 30 metres. Data rate is dependent on channel and peripheral controller design and can be up to 2Mbyte per second.

### **External Store Interface**

The connection to a store from a CPU is via a store link which consists of a store port board (fitted in the store), cable and store link board. The external interface is a cable connection to the store link. The cable may be up to 4 metres long. Maximum data rate with 550ns store is 3.6M bytes per second, and with 800ns store is 2.5M bytes per second.

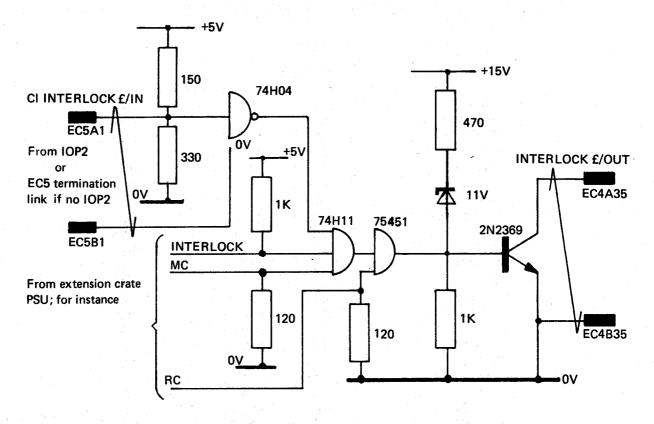

The external store interface enables the user to provide a special Input Output Processor (IOP) operating directly into store. It needs to be supplemented by the Command Interface to provide program control, interrupts and interlocking of store operations associated with the IOP.

### 3.1 GENERAL INFORMATION

The Normal Interface (NI) is the standard input/output interface. The low speed external interfaces such as the V24 interfaces are controlled by peripheral controllers (e.g. asynchronous modem interfaces) connected to a Normal Interface. The device controlling the NI is called the channel controller. The CPU internal channel controller is called the Basic Multiplexer Channel (BMC).

Generally data transfers are performed autonomously, that is, they proceed independently of the processor, after the program has specified the starting address of the appropriate store data area and the length of the transfer required. Once initiated, an autonomous transfer is controlled by the peripheral controller. Each controller connected to the Normal Interface is allocated a Ready line which determines the controller's priority when requesting service from the BMC. Normally at the end of a data transfer the peripheral initiates a Status Break cycle which transfers peripheral and BMC status information to the store. Then the CPU is interrupted to advise it that the data transfer is completed.

Data may also be transferred to or from a peripheral by program cycles. Data transferred to a peripheral is often used for control e.g. for instructing a peripheral to initiate on autonomous cycle.

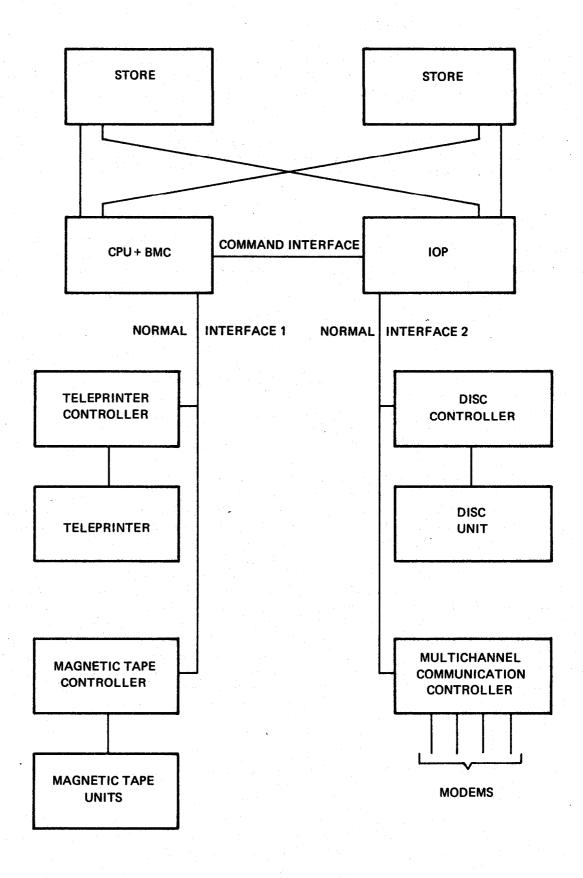

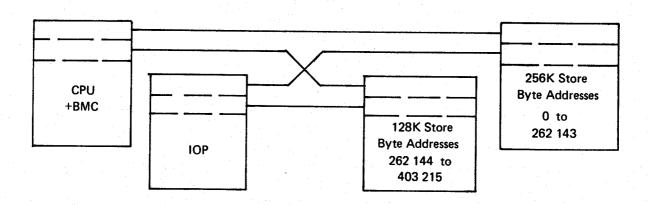

Figure 1 shows possible interconnections between a processor, BMC, IOP and two store modules. In practice the Input/Output load might be handled by the BMC alone.

### 3.2 INTERFACE OPERATION

### Types of Cycle

The channel controller conducts a dialogue known as a cycle with one peripheral controller at a time. There are two main types of cycle:

- (a) Program cycles. These occur at the instigation of the central processor,

- (b) Autonomous cycles. These occur on demand from a peripheral controller, as indicated by an individual READY signal from that controller.

Cycles of either type are allocated by the channel controller, each cycle being divided into subcycles. During each subcycle a subword of 8 or 16 bits is transferred, for peripheral selection or data.

Thus a transfer is the conveyance of data over one or more cycles, each of which is a prescribed sequence of subcycles, with each subcycle providing for the conveyance of one subword.

#### Autonomous Data Transfers

An autonomous transfer is concerned with the sequential output or input of a data string, from or to an area of store. For this the channel controller has access to a number of Way Control Blocks which contain the addresses and sizes of this data string, and other necessary parameters. The Way Control Block is set up by the Nucleus before the autonomous transfer commences. Usually a program cycle is required to cause the peripheral controller to start the autonomous transfer.

The autonomous transfer of the data string normally occupies many autonomous interface cycles, with either a single data subword or a short burst of data subwords being transferred on each cycle. The channel controller may maintain a large number of autonomous transfers in progress simultaneously, allocating cycles to each peripheral as required. Similarly, a particular peripheral controller itself may carry on more than one autonomous transfer simultaneously.

Figure 1: A POSSIBLE SYSTEM INTERCONNECTION

#### Autonomous Status Breaks

An autonomous Status Break transfer is used whenever a peripheral controller wishes to report a significant change of operating circumstances to its controlling software. A change of program may be associated with this interface cycle, which inputs a single operand subword. This is identified with a particular data string and describes the status of the peripheral controller.

Usually Status Breaks are generated as the result of a peripheral controller completing an auton-mous data string transfer. Other uses of Status Break are to report erroneous operation, or to indicate the need for operator (manual) action.

Program Cycles

A program cycle is initiated by a program instruction specifying the direction of transfer and the Way Number. Normally it is used to command or supervise the execution of an autonomous transfer, as noted above. Also it is used explicitly for data transfer, particularly where the peripheral controller is so simple as not to justify the use of the autonomous transfer facility.

Addressing System

Two independent addressing systems are used in the Normal Interface.

The main address is known as the Way Number and lies in the range 0-255. A Way Number corresponds to a separately identifiable source of input data, or destination for output data. A single peripheral controller may use one or more Way Numbers. For example, a paper tape reader uses one Way Number only, whereas a controller for a group of telecommunications lines uses one Way Number per line. A complex peripheral may use one Way Number for data and another for supervisory information.

In program cycles, the software provides a Way Number, which is transmitted by the channel during the first, or select, subcycle. Thus the software uses the Way Number to identify the peripheral concerned. In autonomous cycles the peripheral controller is granted a cycle by the channel and then the peripheral controller itself specifies the Way Number to be used, transmitting this to the channel during the response subcycle of the autonomous cycle. The channel then uses the Way Number to access the appropriate Way Control Block.

The other address is the Ready Number. Each peripheral controller has a unique Ready Number and a corresponding star-connected READY signal. Ready Numbers lie in the range 0-15. When the channel allocates an autonomous cycle, in response to a READY signal raised by a peripheral controller, the channel transmits the corresponding Ready Number in the select subcycle, so initiating a cycle with the peripheral concerned. The peripheral responds with its Way Number, as described above. The Ready Number and READY system are concerned solely with the allocation of autonomous cycles to peripheral controllers in an orderly manner. The subsequent progress of these cycles is determined by the Way Number input by the peripheral, and the Ready Number takes no further part. The Ready Number is not used by, nor is it made available to, the computer program.

Cycle Structure

Normally an interface cycle is made up as described below, though a number of variations can occur in special circumstances:

- (i) A select subcycle is transmitted by the channel controller. This subcycle also specifies the type of transfer required. The subword carries a Way Number in the case of program transfers or a Ready Number in the case of autonomous transfer cycles,

- (ii) A response subcycle is transmitted by the engaged peripheral controller. This confirms engagement. For autonomous transfer cycles, the subword carries the Way Number,

- (iii) An operand-in subcycle is transmitted from the peripheral controller to the channel controller,

- (iv) An operand-out subcycle is transmitted from the channel controller to the peripheral controller.

The actual operand to be transferred is carried by the subwords of subcycles (iii) and (iv), accompanied by control information on the mode lines. In fact, the interface cycles described do not transfer useful operands in both directions, and one of the two subwords carries meaningless data; however the mode lines are needed for control purposes in both subcycles so the subcycle cannot be omitted from the cycle.

The cycle may be extended by repeating subcycles (iii) and (iv) one or more times. This is known as burst mode operation. Burst mode operation increases the useful throughput of the interface, at the expense of increasing the length of the cycles concerned. System **lim**itations impose an upper limit on the cycle length.

### **Interface Signals**

#### Definitions

Interface signals are binary. Their two states are usually referred to as 'true' and 'false'.

All signals are unidirectional. Outgoing signals are generated by the channel controller and inspected by one or more peripheral controllers. Incoming signals are generated by the peripheral controller and inspected by the channel controller.

Star connection describes the situation where an outgoing signal is inspected by, or an incoming signal is generated by, a single particular peripheral controller. Such a signal may be physically present at the connector to other peripheral controllers.

Bus connection describes the situation where an outgoing signal is inspected by many peripheral controllers, or where an incoming signal is the logical 'or' of signals generated by many peripheral controllers. The majority of Normal Interface signals are bus connected, and the electrical specification of internal interfaces allows a distributed 'or' function.

The use of bus connection on incoming lines makes it mandatory that only the peripheral engaged by the select subcycle should place data on these lines.

And-bus connection describes the situation where an incoming signal is the logical 'and' of signals generated by many controllers. One special-purpose signal is connected in this manner. It necessarily uses special transmitter and receiver circuits.

Signal List

| Туре        | Name      | Number | Direction | Connection |

|-------------|-----------|--------|-----------|------------|

| Timing      | OUTTIME   | 1      | Outgoing  | bus        |

| Timing      | ENGAGED   | 1      | Incoming  | bus        |

| Timing      | PROCEED   | 1      | Outgoing  | bus        |

| Timing      | INTIME    | 1      | Incoming  | bus        |

| Information | INFO-OUT  | 16     | Outgoing  | bus        |

| Mode        | MODE-OUT  | 2      | Outgoing  | bus        |

| Information | INFO-IN   | 16     | Incoming  | bus        |

| Mode        | MODE-IN   | 2      | Incoming  | bus        |

| Timing      | READY     | 16     | Incoming  | star       |

| Timing      | PERMIT    | 1      | Outgoing  | bus        |

| Auxiliary   | ACTIVE    | 1      | Outgoing  | bus        |

| Auxiliary   | INTERLOCK | 1      | Incoming  | And-bus    |

#### Interface Expansion

The Normal Interface at logic backplane level as provided directly by a channel controller is called a primary Normal Interface.

A limited number of subunits may be directly connected to the primary Normal Interface, using common power supplies. Each subunit consists of a single logic board or a small number of interconnected logic boards. Simple peripheral controllers are constructed as subunits.

To expand the interface and so accommodate more peripheral controllers, the primary Normal Interface is extended with a Link and an extension unit. An extension unit provides housing and power for peripheral controllers and reproduces the Normal Interface at logic level. A link is in three parts.

- (1) A channel adaptor that connects to the primary Normal Interface.

- (2) A cable.

- (3) A peripheral adaptor that connects to the secondary Normal Interface.

The secondary Normal Interface operates in step with the primary Normal Interface to which it is connected. The timing and logical system used on the secondary interface is identical to that used on the primary interface, except for the degradation in certain fixed time intervals as follows:

i.e. The minimum time periods for the select subcycles, and other signals with a minimum time duration, are less on the secondary interface than are specified for the primary interface.

The effect on the system timing of connecting a link to a primary interface is to cause those controllers on the secondary interface to increase their contribution to the Normal Interface loading by about 10%. Interface loading rules are defined in the System Description manual.

### Multiplexing Links

A link provides an independent set of READY signals for its secondary interface. It combines these READY signals and demands cycles from the channel on one or more primary READY lines. When the channel allocates a cycle to such a primary READY line the link replaces the Ready Number by the appropriate secondary Ready Number for the secondary interface.

### **Timing and Cycle Control**

General

The several subcycles which make up an interface cycle are timed and controlled by the four timing

OUTTIME outgoing generated by channel controller.

ENGAGED incoming, generated by peripheral controller.

Information is transferred over the INFO-OUT, MODE-OUT, INFO-IN and MODE-IN lines. For the purpose of this section INFO-OUT and MODE-OUT are grouped together and called DOUT, and INFO-IN and MODE-IN are called DIN.

signals:

The DOUT lines may be either valid (i.e. carrying meaningful data) or invalid when their meaning is not defined.

The DIN lines may be valid or invalid similarly. There is a further state for the DIN lines, that is false when a peripheral is disengaged, so that there shall be no interference with the operation of other peripherals.

#### Timing

The peripheral transmits its data over the DIN lines accompanied by the two timing signals ENGAGED and INTIME. Whenever the peripheral controller makes the DIN lines valid, it indicates this by a change in a timing signal. Then the peripheral holds DIN, ENGAGED, and INTIME steady until the channel controller acknowledges receipt by changing its timing lines. An exactly similar system is used by the channel controller to indicate when the DOUT lines are valid.

In practice, signals in a parallel group change at marginally different times. This is called 'skew' Such time skew becomes greater whenever the signals are passed through logic stages or over interconnections.

Normal Interface times are measured at the reference connection, where the peripheral connects to the bussed signals. The reference connection is the socket that connects a peripheral controller to the Normal Interface logic level backplane. Signals are so generated that, after allowing for skew, it can be guaranteed, at the reference point that the data is valid at the moment the timing signal changes. Thus any controller attached to a reference connection must allow for skew introduced in its own logic, but not for skew introduced by other equipment.

It is a design feature of the Normal Interface that allowance for skew may be made simply by delaying the timing signals. This may be done up to a limit determined by the channel controller timing.

#### **Ouiescent State**

When no cycle is in progress the interface is maintained in a quiescent state. The channel controller holds OUTTIME and PROCEED false, and all peripherals are disengaged. Disengaged peripherals must hold DIN false, and INTIME and ENGAGED false.

It is required that a peripheral becomes disengaged immediately if the channel controller makes both OUTTIME and PROCEED false, even where this sequence is not compatible with normal operations. This ensures that the interface may be made quiescent even after a transient failure.

The channel controller does not start a cycle until INTIME and ENGAGED are false.

#### Cycle Sequence

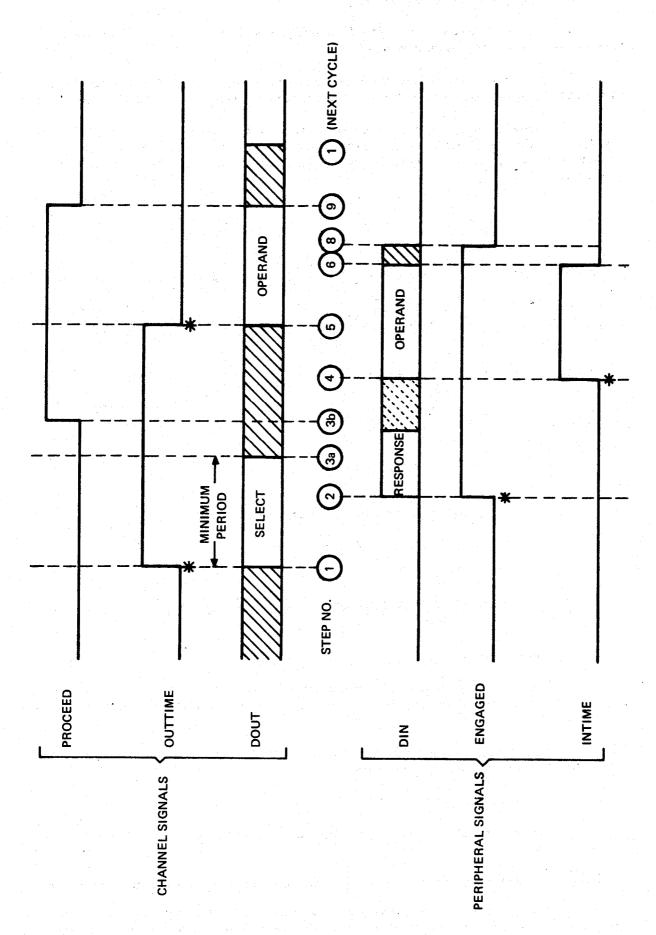

This description of the sequence of events during an interface cycle covers program, autonomous data, and autonomous status cycles, with or without burst operation. To improve clarity, it concentrates on the essentials. Further details are given in the cycle sequence notes A, B, C, D, E following Table 1.

The state of two timing signals is given at each step in Table 1 (see also Figs. 4 to 7); The interface is designed so that only one of the two signals changes state at any significant time, the other remaining unchanged. Thus no problem of skew between timing signals can arise.

The operative timing signal is bracketted, e.g. (OUTTIME).

Thus the notation: '(OUTTIME) true PROCEED false with DOUT valid' indicates that DOUT is made valid, and that OUTTIME then becomes true allowing for skew as previously described.

| Step               | Name           | Action                                                                                                | Notes |

|--------------------|----------------|-------------------------------------------------------------------------------------------------------|-------|

| 0                  | <u>-</u>       | Channel quiescent, all timing signals false                                                           |       |

| 1 Select Channel i |                | Channel initiates cycle, outputs select subword. (OUTTIME) true PROCEED false with DOUT valid.        | Α     |

| 2                  | Response       | Peripheral recognises selection, inputs response subword. (ENGAGED) true INTIME false with DIN valid. |       |

| За                 |                | DOUT may change                                                                                       | В     |

| <b>3</b> b         | Handshake A    | Channel acknowledges responses OK. OUTTIME true (PROCEED) true.                                       | С     |

| 4                  | Operand-in     | Peripheral inputs operand. ENGAGED true (INTIME) true with DIN valid                                  | D     |

| 5                  | Operand-out    | Channel outputs operand. (OUTTIME) false PROCEED true with DOUT valid                                 | D     |

| 6                  | Handshake B    | Peripheral acknowledges operand-out. ENGAGED true (INTIME) false DIN may change                       |       |

| IF THE             | CYCLE IS COMPL | ETE, GO TO STEP 8, OTHERWISE CONTINUE WITH STE                                                        | P 7.  |

| 7                  | Handshake A    | Channel acknowledges Handshake B. (OUTTIME) true PROCEED true DOUT may change                         |       |

|                    | CONDITIONS     | ARE NOW AS FOR STEP 3 CYCLE REPEATS FROM STEP                                                         | · 4.  |

| 8                  | Close B        | Peripheral disengages.<br>(ENGAGED) false INTIME false with DIN zero                                  | E     |

| 9                  | Close A        | Channel disengages OUTTIME false (PROCEED) false DOUT may change                                      | E     |

|                    | ABNORMAL       | TERMINATE (see Abnormal Sequence and Figure 6).                                                       |       |

| 10                 | Reject         | Channel rejects response 2. (OUTTIME) false PROCEED false DOUT may change.                            |       |

| 11                 | Close B        | Peripheral disengages after reject. (ENGAGED) false INTIME false with DIN zero.                       |       |

Table 1: CYCLE SEQUENCE

#### **Table 1 Notes**

- A The combination OUTTIME true, PROCEED false uniquely identifies a select subcycle, and occurs at no other time

- B Step 3a does not occur until at least 300 nanoseconds after step 1 occurs. Channel controllers must be such that periods shorter than this are not presented to the more distant peripherals, even when a nearby peripheral responds very quickly, and OUTTIME is delayed to allow for skew.

- C Following step 3b DIN is invalid for a period as the response subword is removed, and then becomes valid again with the operand subword when INTIME changes (step 4). Peripherals may alter DIN as a result of step 3a (i.e. following change in DOUT). This manner of operation is explicitly permitted and is accommodated by channel controllers.

- In the case of output operand cycles, the INFO-IN lines carry no useful information in step 4, but the MODE-IN lines carry useful information. The unrequired and unspecified data on INFO-IN is nevertheless made valid and timed exactly as though it were indeed useful. Similarly, for input cycles, INFO-OUT lines carry no useful information in step 5, but are made valid and timed correctly.

- E Steps 3 and 9 do not occur in sequence, but both may occur arbitrarily soon after step 6.

Note: if step 8 is very close to step 6, then ENGAGED false may actually procede INTIME false as a result of skew. This is of no importance.

Abnormal Sequence

The sequence described under 'Cycle Sequence' is varied if abnormalities occur:

#### (i) Unacceptable Response

The response subword submitted in step 2 may be unacceptable to the channel for any of a number of reasons, e.g.

Autonomous Data requested is not allowed for the Way Number or the data string is exhausted or is not set up.

Status Break is requested, with PERMIT false.

Peripheral rejects program cycle.

In these cases the channel replies to step 2 by step 10 instead of step 3b, following step 3a. The peripheral must detect this and disengage (step 11).

### (ii) No Reponse

If there is no response step 2 occurs, the channel controller time-outs (see \* below) and goes to step 10 to end the cycle. Since no response has occurred, the conditions of step 11 already obtain. A belated response could possibly still arise, though it is suppressed by step 10 and therefore is transient. The channel allows a delay of at least 3 microseconds to accommodate this transient before a new cycle.

\* For the exact value of the time-out delay refer to the channel controller specifications. The permitted delay from OUTTIME true to ENGAGED true is not less than 30 microseconds with Basic and External Multiplexer Channels.

#### (iii) Other Time-Out Limits

Some channel controllers may in addition apply time-outs of not less than 3 microseconds to the following timing periods:

PROCEED going true to INTIME going true (step 3 to 4)

OUTTIME going false to INTIME going false (step 5 to 6)

OUTTIME going true (step 7 to 4)

As a check that peripheral controllers do not remain engaged for excessive periods, when in burst mode for example, the following overall time-out period of not less than 75 microseconds is used: PROCEED going true to ENGAGED going false (step 3 to 8).

In all cases, if the channel detects a time-out error, it deletes any subword which may be on the interface by making both OUTTIME and PROCEED false. In such circumstances, the peripheral controller which is engaged should likewise delete any subword which is on the interface by making both INTIME and ENGAGED false and dropping INFO-IN and MODE-IN to logic zero. This usually entails the corruption of the data being transferred. In all cases the channel allows a delay of at least 3 microseconds before commencing a further cycle.

### **READY and PERMIT Signals**

READY Signal

If a peripheral controller requires an autonomous cycle it may make its particular READY true at any time, subject to conditions described under PERMIT heading below. The channel controller, in due course, allocates an autonomous cycle to this peripheral in accordance with an inbuilt priority system. The delay between making READY true and a cycle being allocated depends on the relative priority of the peripheral controller and the amount of activity on the channel.

The peripheral controller normally makes READY false when it makes ENGAGED true, but may again set READY, or allow it to remain true, if it requires a further cycle. Such a cycle is allocated in accordance with the priority system in the usual way.

In general, if a peripheral resets a true READY to false at an arbitrary time, it is uncertain whether or not the channel subsequently will allocate an interface cycle with the corresponding Ready Number. To obtain defined results READY should be made false only:

- (a) before ENGAGED is made true during any cycle, addressing the controller concerned,

- (b) within 2 microseconds of PERMIT becoming false, (see under PERMIT signal below),

- (c) on ACTIVE becoming false (see ACTIVE and INTERLOCK Signal, next page).

PERMIT Signal

Autonomous cycles are of two types — data cycles and status cycles. At certain times the channel controller may be unable to process status cycles. The channel controller indicates these times by means of the PERMIT signal which is held true when status cycles are acceptable, false at other times. The PERMIT signal may change state at any time.

When PERMIT is false, no peripheral should raise READY to request a status cycle. Any peripheral with READY true for this purpose when PERMIT goes false, should make its READY false forthwith. The channel controller does not allocate any autonomous cycle during a period of at least 2 microseconds after PERMIT goes false, so allowing time for the READY signals to be removed.

Note that PERMIT is used only to control READY. A peripheral controller which has already started a cycle should not vary its procedure if PERMIT changes.

### **ACTIVE and INTERLOCK Signals**

**General**

The INTERLOCK system is used to protect systems from the effects of erroneous interface signals generated during power sequencing.

A computer system can consist of a number of independently powered units.

When the power supply for a unit is up sequencing or down sequencing, the unit may transmit arbitrary signals over any interfaces connected to it. It is necessary that other units should be prevented from acting upon these signals.

In small systems, loss of mains power to any unit causes the complete system to halt; conversely, sytem operation does not start unless all units have completed up sequencing. In larger systems the system may be partitioned, so tht some units may down sequence or remain off without causing the entire system to cease operation.

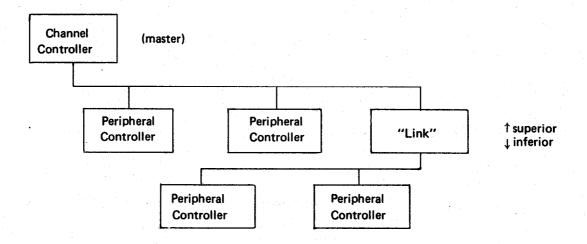

#### Unit Interconnection (see Figure 2)

The interface is hierarchical, and in each case may be said to connect a superior (channel-like) unit to one or more inferior (peripheral-like) units. The superior unit is that which controls the interface, i.e. the unit 'nearer' the processor in simple systems.

A channel controller generally has no unit superior to it. Most ordinary units have one immediately superior unit. It is possible to envisage units which are connected to several immediately superior units, over separate interfaces. A unit with no superior units is referred to in the following sections as a master unit. All other units are slave units.

In the following paragraphs it is assumed, unless otherwise stated, that the system being considered is not partitioned and has only one master unit.

Figure 2: UNIT HIERARCHY

### INTERLOCK Signals

Each independently powered peripheral unit generates an INTERLOCK signal, which is true only if the power supply for the unit is established. In the event of loss of mains, or intentional down sequencing, the unit makes INTERLOCK false at least 1 millisecond before the unit begins to malfunction or to send erroneous interface signals. INTERLOCK itself must be transmitted between independently powered units by a 'power-tolerant' circuit which can maintain a 'false' signal in the absence of power and also during power sequencing.

INTERLOCK must also be made false by any unit which receives a false INTERLOCK from an inferior unit. Where several inferior units are connected via a 'bus', the drive system must generate the logical 'and' of the INTERLOCK signals.

The master unit can form an overall INTERLOCK signal which is true only when the complete system is operational and becomes false at least 1 millisecond before malfunctioning occurs as a result of down sequencing.

When peripheral controllers share a common power supply with the channel controller, or with link hardware via which they are connected, there is no need for them to use the INTERLOCK line as the necessary action in case of supply failure is taken by the channel controller or link hardware as appropriate.

### **ACTIVE Signals**

The master unit generates a signal called ACTIVE, which it transmits to its inferior units.

Any unit receiving ACTIVE as false must:

- (i) Transmit ACTIVE false to any inferiors.

- (ii) Cease operation and enter the reset state.

- (iii) Ignore other signals from its superior, since these may have been incorrectly transmitted.

The ACTIVE signals are transmitted by power-tolerant circuits which can continue to transmit false during sequencing or with no power.

The master normally makes ACTIVE false as soon as it detects overall INTERLOCK false. During switch-on, ACTIVE becomes true.

A master unit may, in response to manual control, make the ACTIVE signals false to cause system reset to occur, even though no power sequencing is involved.

When ACTIVE is made false for any reason it remains in that state for at least 5 /us.

#### **Information and Mode Formats**

General

Tables 2 and 3 which follow show in detail how the 8 or 16 INFO signals and 2 MODE signals in each direction are used, during the various types of interface cycle.

During the SELECT subcycle, MODE-OUT is used to specify the type of cycle allocated by the channel controller as follows:

| MODE - OUT | SELECT Subcycle Type |

|------------|----------------------|

| 00         | Autonomous           |

| 01         | Not used (Spare)     |

| 10         | Program input        |

| 11         | Program output       |

Table 2 shows the continuation of the autonomous cycle, and table 3 deals with the program cycle, Notations are explained in the accompanying notes. The symbol \* is used where INFO-IN signals are ignored by the channel, or where the INFO-OUT signals may take unspecified values. In general operands transmitted via the INFO-IN and INFO-OUT signals may take any values; exceptions are listed below.

| Gycle Class | Subcycle | M INFO-MS  | M<br>7 | L INFO-LS L 7 | MO<br>0 | DE<br>1  | Note |

|-------------|----------|------------|--------|---------------|---------|----------|------|

| Autonomous  | Select   |            |        | Ready Number  | 0       | 0        |      |

| (Data in)   | Response | width mark |        | Way Number    | 1       | . 1      | AD   |

|             | Op-in    | optional   |        | operand       | ×       | X        | В    |

|             | Op-out   | •          |        | <b>*</b>      | У       | <b>y</b> | В    |

| Autonomous  | Select   | *          |        | Ready Number  | 0       | 0        |      |

| (Data out)  | Response | width mark |        | Way Number    | 1       | 0        | AD   |

|             | Op-in    | *          |        | *             | ×       | x        | В    |

|             | Op-out   | optional   | 4.4    | operand       | У       | y        | В    |

| Autonomous  | Select   | *          |        | Ready Number  | 0       | 0        |      |

| (Status     | Response | *          |        | Way Number    | 0       | 1        | D    |

| break)      | Op-in    | optional   |        | status        | 0       | 0        | С    |

| •           | Op-out   | *          |        |               | 0       | 0        |      |

**Table 2: AUTONOMOUS CYCLES**

#### Table 2 Notes:

- A The width mark consists of eight bits and may take the values 00000000 and 10000000 only (i.e. zero or 128). The zero value indicates that the peripheral requires one byte from the data string to be transferred in each subsequent operand subcycle. This occurs by default in the case of 8-bit peripheral controllers. The value 128 indicates that two bytes are to be transferred from the data string in each operand subcycle.

- B The mode bits xx and yy determine whether further cycles or subcycles are possible (see Operand Subcycle MODE Meanings later). The optional m.s. byte of the operand is determined as above.

- C The width of status information is determined by the channel, irrespective of the code transmitted on the m.s. INFO byte during the response subcycle. The l.s. byte of the status information may not be zero ( i.e. 00000000).

- D The MODE-IN code is as follows:

| MODE-IN | Cycle Type              |

|---------|-------------------------|

| 00      | Not used                |

| 01      | Autonomous Status Break |

| 10      | Autonomous Data Out     |

| 11      | Autonomous Data In      |

| Cycle Class                     | Subcycle                              | M INFO-MS M                      | L INFO-LS L               | MODE<br>0 1              | Notes        |

|---------------------------------|---------------------------------------|----------------------------------|---------------------------|--------------------------|--------------|

| Program<br>Input<br>(Accepted)  | Select<br>Response<br>Op-in<br>Op-out | Subaddress<br>*<br>optional<br>* | Way Number  * operand  *  | 1 0<br>1 1<br>x x<br>y y | E<br>EG<br>G |

| Program<br>Input<br>(Rejected)  | Select<br>Response<br>SUBCYLES        | Subaddress<br>*<br>SSUPPRESSED   | Way Number                | 1 0<br>z z               | <b>F</b> .   |

| Program<br>Output<br>(Accepted) | Select<br>Response<br>Op-in<br>Op-out | Subaddress<br>*<br>*<br>optional | Way Number  *  *  operand | 1 1<br>1 1<br>x x<br>y y | E<br>G<br>EG |

| Program<br>Output<br>(Rejected) | Select<br>Response<br>SUBCYCLI        | Subaddress<br>#<br>ES SUPPRESSED | Way Number<br>*           | 1 1 z z                  | F            |

Table 3: PROGRAM CYCLES

### Table 3 Notes

If the peripheral controller is of 16-bits width then all 16 bits are transmitted, and if the m.s. byte is not needed it must be removed by software.

If the peripheral controller is of 8-bits width, the m.s. byte is input as zero.

If the response mode is not 11 the cycle is abandoned by the channel controller as explained under 'Abnormal Sequences'. The MODE-IN code zz is as follows:

| MODE-IN | Response to Program Cycle           |

|---------|-------------------------------------|

| ZZ      |                                     |

| 00      | Reject - underfined fault           |

| 01      | Reject - invalid function           |

| 10      | Reject - peripheral controller busy |

| 11      | Accept                              |

Some channel controllers (e.g. BMC) make zz available to software. Reference should be made to the appropriate channel controller manual for details.

G The Mode bits xx and yy determine whether further cycles are possible, see under 'Operand Subcycle MODE Meanings' which follows: the BMC can transfer only one word in a program cycle, hence it ignores xx and makes yy zero.

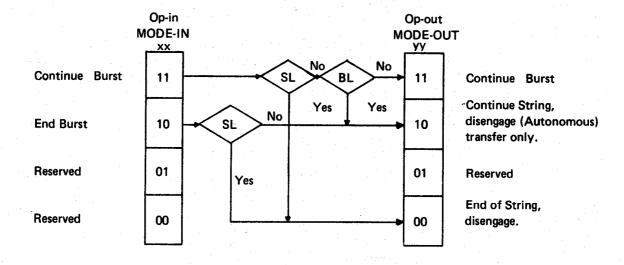

### Operand Subcycle MODE Meanings

The peripheral controller uses MODE-IN during the operand input cycle to indicate its requirement for further subcycles during the present burst.

The channel controller uses MODE-OUT during the operand output cycle to indicate whether further subcycles are to be performed, and in autonomous transfers to indicate when the data string is exhausted.

The codes used are given in Figure 3, which also shows how the channel controller's decision is related to the peripheral controller's request. The channel controller can if necessary end the string or the burst even if the peripheral has requested continuation. Not all channel controllers impose a burst limit other than as an overall time-out.

- SL = String Limit End of data, or Program Transfer Limit

- BL = Burst Limit (Autonomous Transfers only)

Figure 3: OPERAND SUBCYCLE MODE MEANINGS

### **Timing Diagrams**

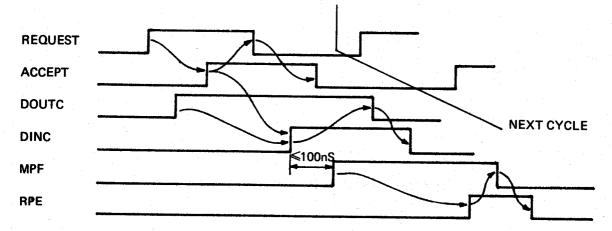

The following figures 4, 5, 6 and 7 illustrate the sequences of events which occur during interface operations. The figures are idealised as regards the detail of signal transitions; they are not to any defined or fixed scale on either axis.

A positive logic convention is used; this does not imply that positive logic is in fact used on the reference version or any other version of the interface.

The following conventions are used:

- Indicates when a signal or set of signals is valid and is to be maintained unchanged in one or other state.

- Indicates when a signal or set of signals is invalid and therefore may be in either state or in transition.

- Indicates the definitive timing signal concerned when more than one signal changes simultaneously; in other words the signal which is in practice delayed to allow for 'skew' (see under 'Timing')

Step numbers shown in the sequences correspond to those listed under 'Cycle Sequence'.

Figure 4: AUTONOMOUS/PROGRAM CYCLE TIMING - SINGLE OPERAND MODE

Figure 6: AUTONOMOUS/PROGRAM CYCLE TIMING - ABNORMAL CONDITIONS

### 3.3 PHYSICAL INTERFACE CONNECTIONS AND SIGNALS

This section describes the basic rules applicable to all peripheral units to be connected to the 16 bit logic level Normal Interface. If the 8 bit version of the interface is being used the references to the most significant byte should be ignored.

#### Circuits

#### **Transmitters**

The open collector driver SN7438 quad two input NAND gate is used generally as the peripheral logic transmitter.

#### Receivers

The standard peripheral logic level receiver is a single logic load input 74N series gate with integral input clamp diodes.

#### **Termination**

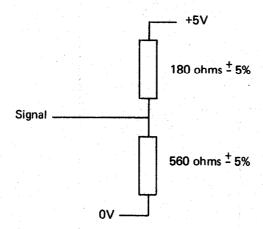

The signal termination network below is used to terminate each signal line:

The termination networks are placed on a termination board at one end of the logic rack for outgoing lines, and on the channel receiver board for incoming lines.

#### Backplane -

The interconnecting backplane consists of a fibre-glass printed circuit board of which two layers are used for the logic level NI. The layer on the surface of the fibre-glass nearest to the logic boards is a signal layer on which the various interface signals are tracked, with earth guard tracks between critical signals. The signal layer is separated by 0.030 inch from a buried earth plane.

The edge connector is a 70 way double sided Type BICC Burndy PB44DD 35-A-02-02 and is designed to fit the standard logic board (see figure 8).

The allocation of NI to the connector pins is shown in Table 4

**COMPONENT SIDE VIEW**

Figure 8: STANDARD LOGIC BOARD

Connector EC1

Connector EC3

|          | В                            | Α                                        | В                                                                            | A               |

|----------|------------------------------|------------------------------------------|------------------------------------------------------------------------------|-----------------|

| 1        | +5V P                        | +5V P                                    | <b>0V</b>                                                                    | INFO-OUT LO £   |

| 2        | -15V P                       | -15V P                                   | INFO-OUT L1 £                                                                | INFO OUT L2 £   |

| 3        | -5V P                        | -5V P                                    | INFO OUT L3 £                                                                | INFO - OUT L4 £ |

| 4        | +15V P                       | +15V P                                   | INFO OUT L5 £                                                                | INFO - OUT L6 £ |

| 5        | OV P                         | 0V P                                     | INFO - OUT L7 £                                                              | MODE-OUTO £     |

| 6        | and the second of the second | gradien German in Jean Stein auch in der | MODE - OUT 1 £                                                               | ov              |

| 7        | 0V                           |                                          | INFO - OUT MO £                                                              | INFO - OUT M1 £ |

| 8        | READY 0 £                    | <b>0V</b>                                | INFO - OUT M2 £                                                              | INFO - OUT M3 £ |

| 9        | 100V 19 at 100               | READY 1 £                                | INFO - OUT M4 £                                                              | INFO - OUT M5 £ |

| 10       | READY 2 £                    | 0V                                       | INFO - OUT M6 £                                                              | INFO - OUT M7 £ |

| 11       | 0V                           | READY 3 £                                | 0V                                                                           |                 |

| 12       | READY 4 £                    |                                          |                                                                              |                 |

| 13       | 0V                           | READY 5 £                                |                                                                              |                 |

| 14       | READY 6 £                    | OV / 15 44                               |                                                                              |                 |

| 15       | <b>0</b> V                   | READY 7 £                                | ang tangkapan Peranggan Peranggan Peranggan<br>Peranggan Peranggan Peranggan |                 |

| 16       | READY 8 £                    | 0V                                       |                                                                              |                 |

| 17       | <b>0V</b>                    | READY 9 £                                | 0V                                                                           | INTERLOCK       |

| 18       |                              |                                          |                                                                              |                 |

| 19       | 0V                           | READY 10 £                               |                                                                              |                 |

| 20       | READY 11 £                   | 0V.                                      | ta najgrina we v                                                             |                 |

| 21       | 0V                           | READY 12 £                               |                                                                              |                 |

| 22       | READY 13 £                   | 0V:                                      |                                                                              |                 |

| 23       | 0V                           | READY 14 £                               | OUTTIME C                                                                    | 0.4             |

| 24       | READY 15 £                   | 0V<br>0V                                 | OUTTIME £                                                                    | 0V<br>ENGAGED £ |

| 25<br>26 | OV<br>INFO IN LO £           | INFO-IN L1 £                             | PROCEED £                                                                    | OV ENGAGED E    |

| 26<br>27 | INFO-IN LO E                 | INFO-IN L3 £                             | OV E                                                                         | INTIME £        |

| 28       | INFO-IN L4 £                 | INFO-IN LS £                             | PERMIT £                                                                     | 0V              |

| 29       | INFO-IN L6 £                 | INFO IN L7 £                             | 0V                                                                           | ACTIVE £        |

| 30       | INFO-IN L8 £                 | INFO-IN L9 £                             |                                                                              | 0V              |

| 31       | 0V                           | INFO - IN MO £                           | 0V P                                                                         | OV P            |

| 32       | INFO - IN M1 £               | INFO - IN M2 £                           | +15V P                                                                       | +15V P          |

| 33       | INFO - IN M3 £               | INFO - IN M4 £                           | -5V P                                                                        | -5V P           |

| 34       | INFO - IN M5 £               | INFO - IN M6 £                           | -15V P                                                                       | -15V P          |

| 35       | INFO - IN M7 £               | ov                                       | +5V P                                                                        | +5V P           |

|          |                              |                                          | •                                                                            |                 |

|          | <u> </u>                     | 1                                        |                                                                              | 1               |

Edge connector pin numbers

P = Power Rail

**Table 4: NI LOGIC LEVEL CONNECTIONS**

### Signal Polarity

Negative logic convention is used on the backplane NI:

Logic FALSE (0) >+ 2.5V i.e. HIGH voltage level Logic TRUE (1) <+ 0.5V i.e. LOW voltage level

Indication is by the "£" sign after the signal name. One signal, INTERLOCK, is an exception to the negative logic convention.

### **Engineering Restrictions**

The board track length of the signals should not exceed 3 inches and should be guarded by an earth track running parallel to and separated by 0.050 inch from the signal track for as much of its length as possible. The earth track should be connected to the logic board earth close to the relevant transmitter or receiver package.

Parallel running of any information or mode signal to a timing or auxiliary signal should be avoided.

#### **Power**

The power pin connections to a peripheral logic board are standard.

There are four voltage rails available, +5V, +15V, -15V, and -5V. The +5V and -5V rails have a maximum variation of 0.2V, the +15V and -15V rails have a maximum variation of 2V.

The ± 5V rails are established before and fall after the ± 15V rails.

### 4.1 GENERAL INFORMATION

The External Link (EL) provides a version of the Normal Interface to which a user can connect a peripheral controller or controllers without being constrained by the GEC Computers Ltd. mechanical standards. It is a cable, as opposed to a backplane, defined Normal Interface.

The Peripheral Link consists of a channel adaptor board, a cable, and a peripheral adaptor board. The latter produces a secondary logic level interface up to 100 ft. from the channel or primary Normal Interface. The EL is supplied less the peripheral adaptor board with a choice of cable lengths from 10 ft to 100 ft.

READY lines are multiplexed onto a single line within the peripheral adaptor board. This single-line is patched on the channel adaptor board connected to the Normal Interface. Hence there is only a single READY line on the cable defined EL.

#### 4.2 LOGICAL OPERATION

The logical operation is defined in the Normal Interface section of this manual. There are some differences, however, which are described below:

#### **FAST OUTTIME**

This is an additional signal required for the peripheral adaptor board and is used to statisise the READY lines on the secondary Normal Interface. It should not be used in place of OUTTIME when connecting directly to the interface.

#### **OUTTIME, INTIME and ENGAGED**

These control signals are delayed by the channel adaptor to allow for their inherent transmission delay differentials in the Link.

ME

This signal is generated by the channel adaptor when the patched encoded Ready Number corresponds with the data output lines. It is used by the peripheral adaptor during the select phase of an autonomous cycle. This signal is not required if the encoded Ready Number is recognised within the user's peripheral controller.

#### LINK ENABLE AND DISENABLE

The channel adaptor contains logic which enables a user's peripheral to isolate itself from the host system. This facility can be used in three ways:

- (a) To isolate the user's peripheral or peripherals from the host system.

- (b) To allow either of two sets of user peripherals to be connected to the host system,

- (c) To permit a user's peripheral to be switched between two or more processors.

NOTE: (b) and (c) above imply the use of multiple interface links.

Normally the ENABLE signal is held true. When it goes false the channel adaptor prevents the incoming signals from the external interface reaching the logic level NI. When the user peripheral sets ENABLE true, the EL is not connected to the NI until at least 5 µs have elapsed after the logic level NI has finished its correct cycle.

When the ELis used without the peripheral adaptor board, the logic on the channel adaptor board allowing faster data transfers in burst mode must be disabled by the fitting of a wire link.

#### **INTERLOCK**

The channel adaptor board can be patched to prevent INTERLOCK from the EI reaching the NI. When this is done a permanently true INTERLOCK is transmitted to the NI.

#### **Data Latches**

The state of the 16 INFO-OUT lines and the 2 MODE-OUT lines from the NI is maintained on the channel adaptor board while OUTTIME is true.

### 4.3 IMPLEMENTATION

The channel adaptor board is a GEC Computers Ltd. standard logic board with transmitters, receivers etc. mounted on the board in dual-in-line packages. The 8 bit Normal Interface requires one cable connected to the board. The 16 bit version requires two cables.

Each cable contains 37 twisted pair conductors (34 of which are used) with overall screening. Each end is terminated with a standard shrouded B.I.C.C. Burndy PB4DD 35-02-02 connector. The cable length is specified by the customer up to 100 ft.

A balanced transmitter/receiver system is used which gives a common mode noise immunity of 10 volts.

#### **Transmitter**

This is a Texas SN75183 or a National Semiconductor DM8830N with the following specifications:

**Package**

14 pin Dual - in - line

Type

Dual differential line driver

Logic

Dual 4 input NAND or AND depending on the output conditions

**Power Supply**

+5V, 36 mA internal consumption

per each driver:

80 mA external drive.

Input Load

3 Normal TTL loads (4.8 mA max.)

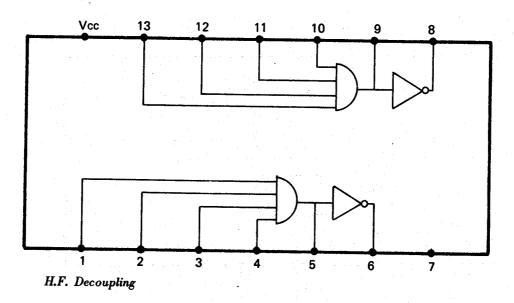

The package functional logic diagram and package connections are shown below:

Each transmitter package requires 0.01 µF decoupling capacitor from Vcc to ground, located in the area occupied by the transmitter.

#### Receiver

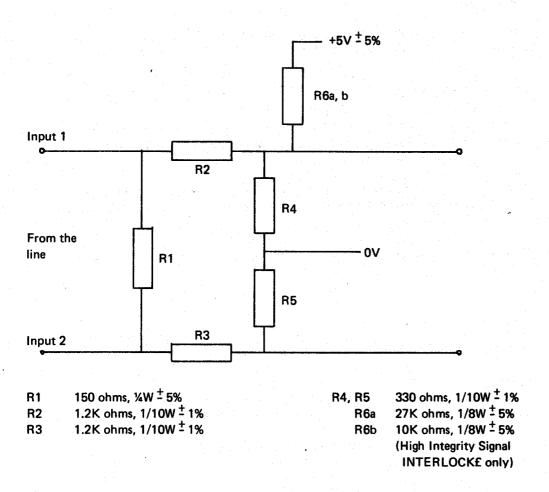

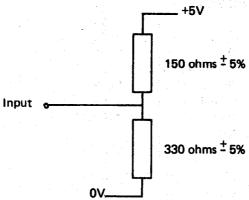

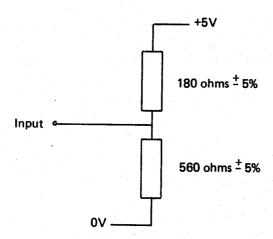

The differential line receiver is used with a termination network on its input. In addition to terminating the lines, the network provides an input attenuation of 4.6:1 and fail safe biassing of the receiver. The termination network is shown below:

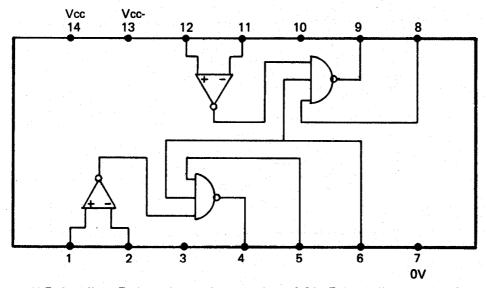

To keep circuit delays to a minimum, the network should be fitted as close as possible to the receiver with a tracking length of less than 2 in. The receiver function logic diagram is shown below:

H.F. Coupling. Each receiver package requires a 0.01 µF decoupling capacitor from Vcc to ground and a 0.005 µF decoupling capacitor from -Vcc to ground, both located in the area occupied by the receiver package. 28

Receiver type no. : Texas SI

Texas SN75107 or SN75108 (open collector)

Туре

**Dual differental line receiver**

Logic

Dual 3 input NAND (one input common)

Power requirements :

+5V, 30 mA max. per dual circuit -5V, -15 mA max. per dual circuit

Output Load

10 Normal TTL loads

# Link Delays from Input to Transmitter to Output of Receiver

|                          | Min.(ns) | Typical (ns) | Max<br>16 | . (ns) |

|--------------------------|----------|--------------|-----------|--------|

| Transmitter SN75183      | 6        | 12           |           | / 4 \  |

| 100 ft. cable            | 143      | <br>150      | 157       | (A)    |

| Attenuator to Receiver - |          |              |           |        |

| threshold.               | 8        | 9            | 10        |        |

| Rise time allowance      | 0        | <u>-</u>     | . 8       | (B)    |

| Receiver SN75107         | 10       | <u>17</u>    | 25        |        |

| Total (ns)               | 167      | 188          | 216       |        |

- (A) The cable allowance is 1.5 ns/ft. delay plus 0.15 ns/ft skew

- (B) Due to 1.5V differential noise immunity

## **Signal Timing**

At their respective transmitter inputs on the channel adaptor board:

- (a) INFO-OUT and MODE-OUT are established a minimum of 68 ns before OUTTIME goes true,

- (b) INFO-OUT and MODE-OUT are maintained for a minimum of 58 ns after OUTTIME goes false,

- (c) ME is established a minimum of 36ns before OUTTIME goes true.

At their respective outputs on the channel adaptor board:

(a) INFO-IN and MODE-IN must be established a maximum of 46 ns after ENGAGED goes true or INTIME goes true.

### Screening and Earthing

The interface cable incorporates an overall copper braid screen with provision for earthing at both ends. 30in. long flying leads are connected to the copper braid so that they can be earthed to the 'Safety Earth' studs of the cabinets at each end of the cable. The cable screen and the cabinets provide a continuous screen around the signal transmission paths.

Several conductor pairs in each interface cable are allocated for logic OV connection.

#### **Cable Connections**

One cable, connected to EC4 on the channel adaptor board, carries all the signals for the 8 bit Normal Interface. For the 16 bit Normal Interface an additional, mechanically similar, cable is connected to EC6. The allocation of signals to the edge connectors is shown in Table 5

### Signal Levels

On the cable a signal is true when it is greater than 1.8 volts positive relative to its inverted signal (labelled with a £ sign).

i.e. OUTTIME is true if:

As the transmitter/receiver system is a balanced one, OUTTIME is false if:

#### Cable connected to EC4

Cable connected to EC6

|    | В               | Α                                     | В               | Α             |

|----|-----------------|---------------------------------------|-----------------|---------------|

|    |                 |                                       |                 |               |

| 1  | 0V              | <b>0</b> V                            |                 |               |

| 2  |                 | INTERLOCK                             |                 | •             |

| 3  |                 | READY M                               | INFO - OUT M7 £ | INFO - OUT M7 |

| 4  | 0V              | 0V                                    | INFO - OUT M6 £ | INFO - OUT M6 |

| 5  | INTIME          | INTIME £                              | INFO - OUT M5 £ | INFO - OUT M5 |

| 6  |                 | ENGAGED                               | INFO - OUT M4 £ | INFO - OUT M4 |

| 7  |                 | ACTIVE                                | INFO - OUT M3 £ | INFO - OUT M3 |

| 8  | PERMIT          | PERMIT £                              | INFO - OUT M2 £ | INFO - OUT M2 |

| 9  | PROCEED         | PROCEED £                             | INFO - OUT M1 £ | INFO - OUT M1 |

| 0  | OUTTIME         | OUTTIME £                             | INFO - OUT MO £ | INFO - OUT MO |

| 1  | ENABLE #        | · · · · · · · · · · · · · · · · · · · | INFO-IN M7      | JNFO-IN M7    |

| 2  | FAST O/T        | FAST O/T £                            | INFO-IN M6      | INFO-IN M6    |

| 3  | ME f            | : ME                                  | INFO-IN M5      | INFO-IN M5    |

| 4  |                 |                                       | INFO-IN M4      | INFO-IN M4    |

| 5  | MODE - OUT 1    |                                       | INFO-IN M3      | INFO-IN M3    |

| 6  | MODE - OUT 0    | MODE - OUT 0                          | INFO-IN M2      | INFO-IN M2    |

| 7  | INFO OUT L7     | INFO - OUT L7                         | INFO-IN M1      | INFO-IN M1    |

| 3  | KE              | YWAY                                  | KEY             |               |

| 9  | INFO OUT L6     | INFO - OUT L6                         | INFO IN MO      | INFO-IN MO    |

| וכ | INFO - OUT L5   | INFO OUT L5                           |                 |               |

| 1  | INFO OUT L4     | INFO - OUT L4                         |                 |               |

| 2  | INFO - OUT L3 £ | INFO - OUT L3                         |                 |               |

| 3  | INFO OUT L2 £   | INFO OUT L2                           |                 |               |

| H  | INFO - OUT L1 £ | INFO - OUT L1                         |                 |               |

| 5  | / INFO-OUT LO £ | INFO OUT LO                           |                 |               |

| 3  | MODE - IN 1     | MODE-IN1 £                            |                 |               |

| '  | MODE - IN 0     | MODE-INO £                            |                 |               |

| 1  | INFO - IN L7    | INFO-IN L6 £                          |                 |               |

|    | INFO - IN L6    | INFO IN L6 £                          |                 |               |

|    | INFO - IN L5    | INFO-IN L5 £                          |                 |               |

| ŀ  | INFO - IN L4    | INFO · IN L4 £                        |                 |               |

|    | INFO - IN L3    | INFO · IN L3 £                        |                 |               |

|    | INFO - IN L2    | INFO-IN L2 £                          |                 |               |

|    | INFO - IN L1    | INFO-IN L1 £                          |                 |               |

| ;  | INFO - IN LO    | INFO-IN LO £                          |                 |               |

**CONNECTION PIN NUMBER**

£ = inverted signal

This section of the manual defines the logical operation of the Store Interface as seen from a processor and its implementation.

#### 5.1 GENERAL INFORMATION

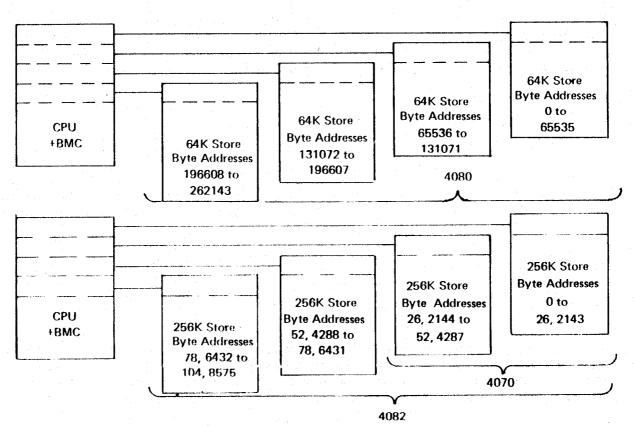

4080 store units have a capacity of either 32K or 64K bytes. The 4070 store unit can be fitted with any multiple of 32K bytes up to a maximum of 256K bytes. The capacity of the 4082 store unit is 128K or 256K bytes. Data is read or written in either bytes (8 bits) or halfwords (16 bits). Each byte has an associated parity bit which is added to the byte on writing and has its validity checked on reading. This is carried out within the store unit. A 4080 unit may be accessed by up to 4 processors on a fixed priority basis; while a 4070 or 4082 store unit may be accessed by up to 6.

#### 5.2 SYSTEM ASPECTS

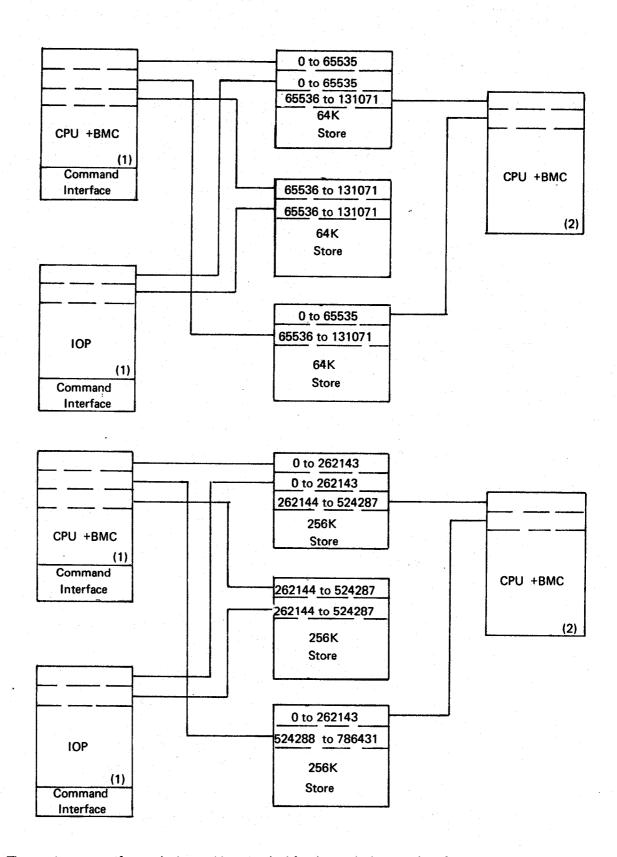

The simplest possible store configuration is shown below:

The Store Link plugs into the CPU backplane at one end and the store unit backplane at the other end. It consists of 2 logic boards and interconnecting cables. The processor contains store slots, and therefore it can be connected to store units to give access to the maximum core store size as shown below:

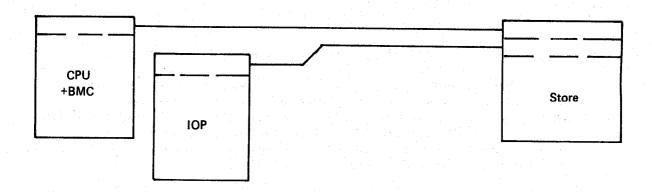

If a second processor or Input/Output Processor (IOP) is included in a system then the configuration shown below is needed.

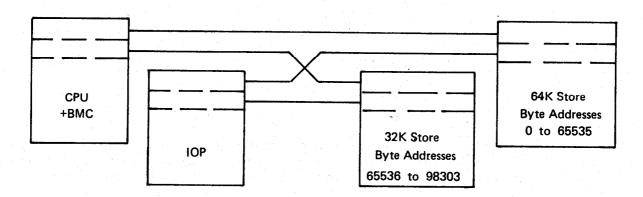

If the system is expanded to include two stores, as shown below, both the CPU/BMC and the IOP access the store simultaneously, provided that they do not wish to access the same store unit.

In the configuration shown above the CPU/BMC can be accessing the 64K byte store unit while the IOP is accessing the 32K byte store unit. In theory this permits a doubling of the effective store data transfer rate. In practice, since both processors must access the 64K byte store unit from time to time to access the Way Control Blocks the achievable data transfer rate is always less than the theoretical maximum.

In the configuration shown above the CPU/BMC can be accessing the 256K byte store unit while the IOP is accessing the 128K byte store unit. In theory this permits a doubling of the effective store data transfer rate. In practice, since both processors must access the 256K byte store unit from time to time to access the Way Control Blocks the achievable data transfer rate is always less than theoretical maximum.

Since the store address patching is carried out on the board at the store end of the Store Link there is no necessity for each processor to address the various store units in the same manner, as shown below: If two processor-like devices (e.g. CPU and IOP) make simultaneous store requests then, normally, the IOP is given priority over the CPU. Priority is determined by the slot position in the store unit, into which the interface link is plugged - Slot 7 (or 4) has the highest priority, slot 2 (or 1) has the lowest priority. Store starting addresses are patchable in increments of 32KB.

NOTES: The number range refers to the byte address patched for the particular store interface.

## 5.3 INTERFACE OPERATION

Data is transferred between the processor and the store over two highways. Each highway is 2 bytes wide. Data is transferred in either bytes or halfwords (two bytes).

Transfers from the processor to store are called output transfers, and the data is transferred over the output data highway. The two bytes are identified as DOUTM and DOUTL. Byte transfers are carried out on DOUTL. For halfword transfers DOUTL is the less significant byte.

Transfers from the store to the processor are called input transfers. The two bytes transferred over the input data highway are identified as DINM and DINL.

For both highways bit 0 is the most significant bit. The 4080 processor can address up to 256K bytes of store. To do this there are 18 address bits. These are called XADD/14,15 and ADDR/0 to 15. The 4070 processor can address up to 512K bytes of store with 19 address bits. These are called XADD13 to 15 and ADDR/0 to 15. And the 4082 processor can addresses up to 1M byte of store with 20 address bits. These are called XADD 12 to 15 and ADDR/0 to 15. For halfword transfers ADDR/15 is always zero. For byte transfers ADDR/15 determines which byte in the halfword is selected. When true the least significant byte is addressed.

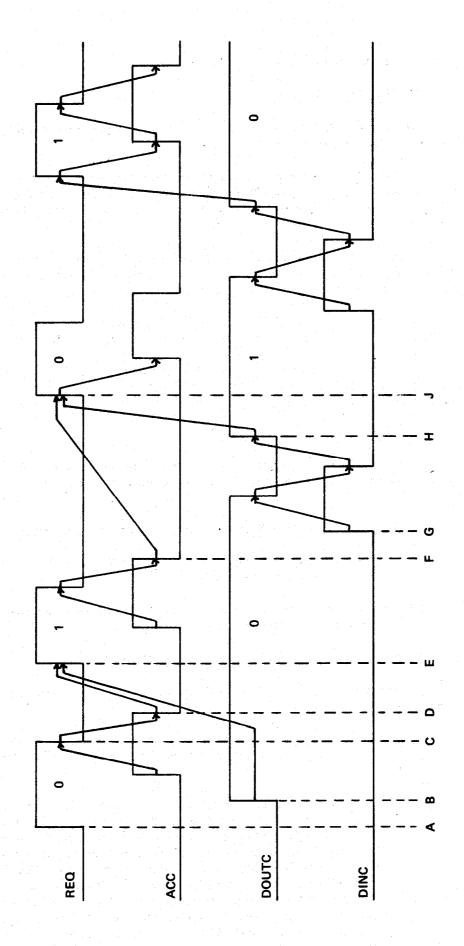

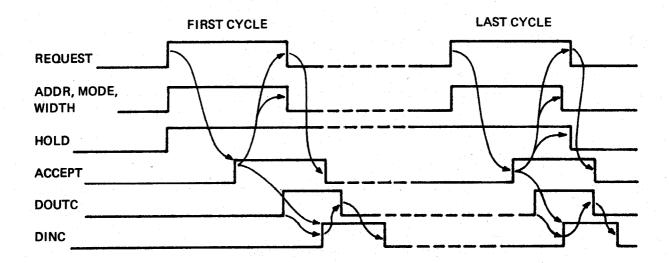

### **Store Cycles**

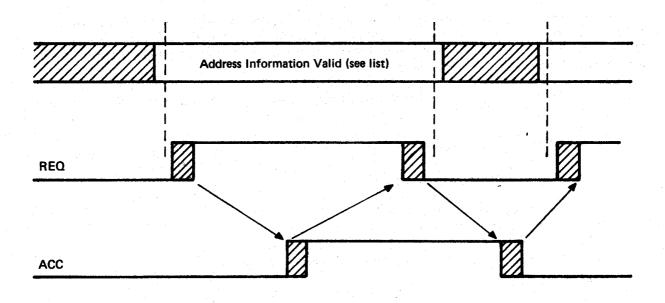

Each store cycle consists of two part-cycles, the address part and the data part. Each part-cycle has a separate and independent handshake of timing signals. The CPU initiates a transfer by setting REQUEST (REQ) true. This is acknowledged by the store generating ACCEPT (ACC). Similarly the data part-cycle is controlled by the DOUTC and DINC handshake. It is not necessary to complete one data part-cycle before starting the next address part-cycle. Consequently it is necessary to distinguish between consecutive part-cycles. This is done by the REQSEQ and DOUTSEQ lines. These have defined values, known as the sequence number, at times related to REQ and DOUTC and are used to associated each data-cycle with the appropriate address part-cycle.

The interface also contains various signals related to error detection, power sequencing and store interface monopolisation.

## Address Part-cycle

Before the processor initiates a store cycle it establishes the XADDR, ADDR, MODE, WIDTH and REQSEQ lines, thus specifying the required store location, the type of transfer (input or output) the width of the transfer (byte or half-word) and the sequence number (0 or 1). The address part-cycle is timed by REQ and ACC as shown in figure 9. REQ and ACC form a strict handshake, the following sequence being always observed:

| (i)   | REQ | becomes true  |

|-------|-----|---------------|

| (ii)  | ACC | becomes true  |

| (iii) | REQ | becomes false |

| (iv)  | ACC | becomes false |

The outgoing information transmitted from the processor to the store during the address part -cycle is:

| 4080<br>XADD 14, 15<br>ADDR 0 to 15 | 4070<br>XADD 13, 14, 15<br>ADDR 0 to 15 | 4082<br>XADD, 12, 13, 14, 15<br>ADDR 0 to 15 | Address                                                                 |

|-------------------------------------|-----------------------------------------|----------------------------------------------|-------------------------------------------------------------------------|

| Width                               | Width                                   | Width                                        | 0 for byte, 1 for halfword                                              |

| MODE<br>REQSEQ                      | MODE<br>REQSEQ                          | MODE<br>REQSEQ                               | 0 for read, 1 for write<br>Alternately 0 and 1<br>on consecutive cycles |

This information is held valid by the processor while REQ is true.

|                         | 4080       | <u>4070</u> | 4082       |

|-------------------------|------------|-------------|------------|

| Address Information is: | ADDR/0-15  | ADDR/0-15   | ADDR/0-15  |

|                         | XADD/14,15 | XADD/13-15  | XADD/12-15 |

|                         | WIDTH      | WIDTH       | WIDTH      |

| •                       | MODE       | MODE        | MODE       |

|                         | REQSEQ     | REQSEQ      | REQSEQ     |

Figure 9: ADDRESS PART-CYCLE TIMING

### Data Part-cycle

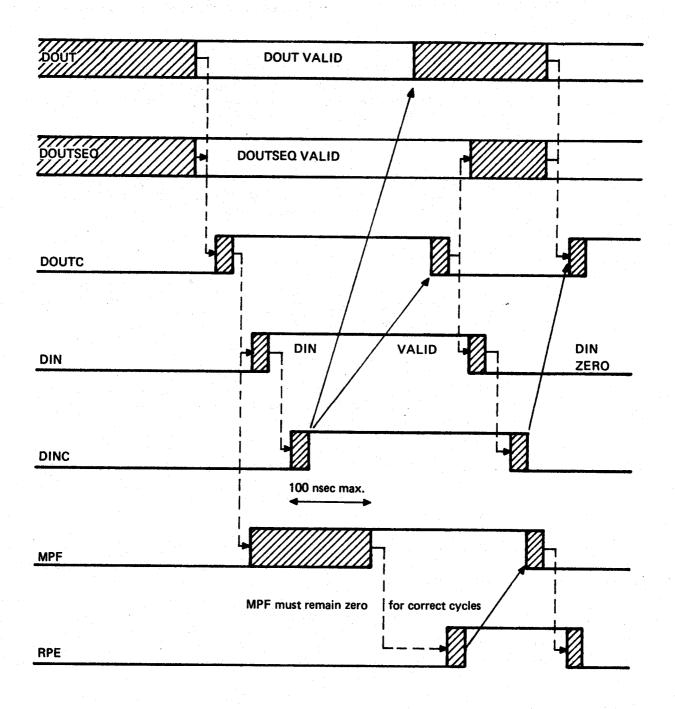

The control signal handshakes are identical for both the input and output data transfers, although there are differences in the time relationship between the signals in the two cases. The transfer of data is controlled by the DOUTC/DINC handshake. Essentially data output to the store is valid between the leading edge of DOUTC and the leading edge of DINC. Data input from the store is valid between the leading edge of DINC and the trailing edge of DOUTC.